ステップアップ形DC/DCコンバーターの設計(2)使用する部品の定格:たった2つの式で始めるDC/DCコンバーターの設計(9)(1/4 ページ)

今回はステップアップコンバーターに使用する部品の定格について説明、検討していきます。

前回は主にUSB駆動機器や1次電池、2次電池など入力電圧の種別が限られる機器で使用されるステップアップコンバーターの基本動作について説明しました。その名前の通り入力電圧より高い出力電圧が得られるステップアップコンバーターの出力電圧Voutは1/(1−δ)に比例し、また昇圧比が高くなるにつれてコンバーターの利得が高くなることも説明しました。

今回はこのステップアップコンバーターに使用する部品の定格について前シリーズのステップダウン形DC/DCコンバーターにならってその要点について説明、検討していきます。説明が足らない箇所についてはステップダウン形DC/DCコンバーターの説明を参照してください。

半導体の要求定格

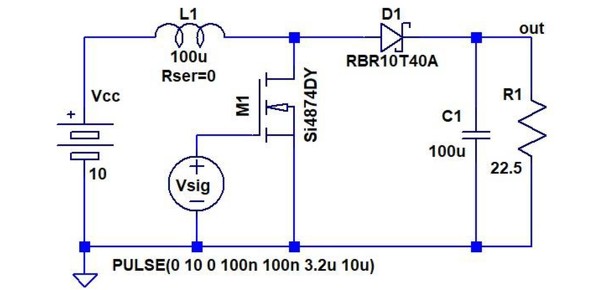

ここでは理想化された回路図ではなく、実際の回路に近い図1や図6の波形を元に各部品の要求特性について考えます。

FET(M1)

FET-SWオフ時には回路説明の項で述べたように次の現象が発生します。

“このようにオン時とオフ時では電流の流れの一部が切り替わります……”

一方、実際の機器では有限長の配線(導線)が存在し、この導線には回路図には表れない寄生(浮遊)インダクタンスLeが付随して発生します。

先に述べたように、電流の流れが急に切り替わると各電流経路の寄生インダクタンスLeを原因としてLの式(E=L×ΔI/Δt)によるスパイク電圧がLeの両端に発生します。

またFETがオン、オフして回路電圧が急変すれば回路につながっている部品の寄生容量への充放電電流がCの式(I=C×ΔV/Δt)に従ってヒゲ状の電流になって流れます。

特に図2に示すようにFETのターンオン時に流れる電流をターンオンピーク電流IdMとします。

FETのドレイン−ソース間にCRスナバー回路(=次回説明予定)を付加した時のスパイク電圧については次回説明するようにある程度計算することもできます。ですが精度の点では目安や傾向に留めておく程度の精度しか得られていません。

実際の設計では経験則による補正も含めて次のような設計手順が主に用いられています。

VDSS:FETのドレイン−ソース間の最大定格電圧です。M1がターンオフするとFETのドレイン(D)は[出力電圧Vout+VF(D1)]になります。したがってFETのD-S間には(Vout+VF)の電圧が印加されますが、この値は理論値です。

実際には各素子やパターンのLeによって(Vout−VCC)程度のスパイク(リンギング)電圧が*上乗せされて印加されるのでFETのVDSSはこのスパイク電圧に対してマージンを取らなければなりません。

VDSS定格として(Vout−VCC+Vout+VF≒2Vout−VCC)の1.25(=1/0.8)倍を考えればよいでしょう(80%ディレーティング)。Voutは定電圧制御が機能して一定なので1式から入力電圧VCCの下限が低いほどVDSS定格の要求は大きくなります。この最低入力電圧をVCC(MIN)とするとVDSSの要求値は1式になります。

*FETのVDSS定格電圧が許せばスパイク電圧は抑制しない方がコンバーターの変換効率は高くなりますがノイズや他回路へのノイズの影響を考慮すると一般には1式程度に抑制するようにCRスナバー回路などが付加されます。

Id(DC):FETのドレイン定格電流Id(DC)です。

ドレイン電流の各部の波形の名称を図2に示します。

M1のドレインに流れる電流Idは既に説明したように、“入力電流Iin+(ΔI)/2”がオン期間tonに流れます。この値がIdpです。

ただしこの値は理論値であり、実際のFETのターンオン時に前述のヒゲ状のターンオンピーク電流Id Mが重畳されます。ですが、この項目については前回のステップダウン形DC/DCコンバーターの章で説明したようにドレイン電流のパルス定格Id(Pulse)が定義、保証されているので測定値IdMはId(Pulse) の80%に収まっていれば問題ありません。したがって必要な電流定格の値は次の2式、3式の値にします。

3式のIdPは

ですからδ→0でIdP=Ioとなり、δの増加に従ってIdPは増加していきます。したがって3式はδが大きくなる、つまり入力電圧VCCが最低になる条件で判断します。

上記の2式のIdMはCRスナバー回路が付加された場合は(2VoutーVCC)/R2で計算されるピーク電流が流れる時があり、加えて後段の整流ダイオードD1の寄生容量CAKも含めて計算しなければなりません(R2はCRスナバー回路の抵抗値)。

このCAKは電圧依存の非直線性特性を持つので計算は困難です。一般にはIdMは実測で求めて、その値から周辺定数を調整します。

Copyright © ITmedia, Inc. All Rights Reserved.