低速読み出しフラッシュメモリでも、CPUが高速動作できる工夫とは?:Q&Aで学ぶマイコン講座(109)(2/3 ページ)

マイコンユーザーのさまざまな疑問に対し、マイコンメーカーのエンジニアがお答えしていく本連載。今回は、初級者の方からよく質問される「低速読み出しフラッシュメモリでも、CPUが高速動作できる工夫とは?」についてです。

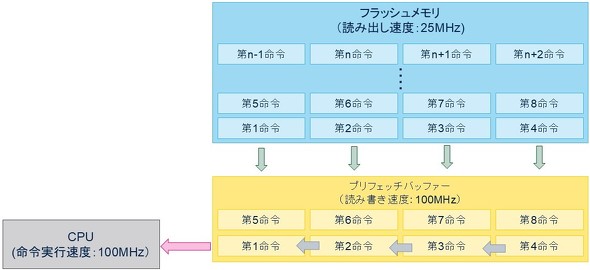

FIFO方式(プリフェッチバッファー)

フラッシュメモリから読み出した命令を、いったんマイコン内部のFIFOに格納し、順次FIFOから命令を読み出して実行します。FIFOとは「先入れ先出し」のバッファーメモリです。FIFOのメモリセルはRAMと同じような構造なので、高速書き込み、高速読み出しが可能です。先に読み込んだ命令を、読み込んだ順から読み出す構造になっています。容量は製品の仕様によって決まります。

フラッシュメモリから読み出した命令を、いったんマイコン内部のFIFOに格納する動作をプリフェッチと呼びます。そして、FIFOをプリフェッチバッファーと呼びます。フラッシュメモリの読み出し速度がCPUの演算速度に比べて遅い時の対応策の1つです。具体的な構成や仕様は、各マイコンメーカーの企業秘密になるので、一般的な概念だけ解説します。

プリフェッチバッファーは読み込んだ命令の順番に従って命令をCPUに送ります。読み込んだ128ビットの4命令を4つに分割して、最初の命令から順次CPUに送ります。CPUの演算速度はフラッシュメモリの4倍ですので、ちょうど4命令を実行している間に、次の4命令をフラッシュメモリから読み出してプリフェッチバッファーに格納できます。この一連の動作によって、CPUは連続して命令を実行できます。

コラム

FIFOを使ったプリフェッチ方式は、新しい方式ではありません。まだ、マイコンにフラッシュメモリなどの命令用のROMが内蔵される前からある方式です。外部の命令用ROMから読み出した命令を、いったんマイコン内部のプリフェッチバッファーに格納し、順次読み出して実行します。これは外部のROMの読み出し速度がCPUの演算速度よりも遅いためです。プリフェッチバッファーを使わずに小さいRAMを使う場合もあります。具体的な構成や仕様は、各マイコンメーカーによって異なりますが、基本的な仕組みは同じです。

最近のマイコンは、1命令1サイクルで実行されますが、昔のマイコンは、1命令を数サイクルで実行したため、命令実行サイクル中に、次の命令をFIFOに読み込むことができました。

今回解説する方式は、外部の命令ROMを内蔵フラッシュメモリに置き換えたものです。

ちなみに、筆者が約40年前に設計したマイコンは、外部に命令用ROMを並列につないで、プリフェッチバッファーに読み込む方式でした。

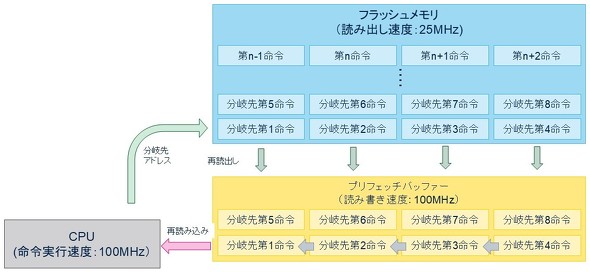

分岐障害

プリフェッチ方式は、非常に便利な仕組みだと言えますが、大きな弱点があります。それは、分岐です。分岐が発生すると飛び先のアドレスの命令はプリフェッチバッファーに入っていませんので、フラッシュメモリから新たに読み出さなくてはなりません。そして、せっかくプリフェッチバッファーに取り込んでおいた命令を破棄しなくてはなりません。

プリフェッチバッファー方式で分岐が頻繁に起きると、命令実行が一時停止を繰り返し、演算効率が落ちます。

身近な例ではソフトウェアタイマが挙げられます。ソフトウェアタイマーの場合、分岐しながら同じ命令を繰り返しますが、都度フラッシュメモリから読み出し直すことになり、そこでタイムロスが発生し、実行命令数から正確な時間を計算できなくなります。

Copyright © ITmedia, Inc. All Rights Reserved.