ノーコードでPLDを開発できる! 概念設計から試作までをわずか数分に短縮:TIが満を持してPLD市場に参入

システムの高機能化や高度化が進むにつれ、設計を担当するエンジニアは設計の複雑さ、小型・軽量化、開発期間の短縮といった課題を抱えることになる。Texas Instruments(TI)が発表したPLDファミリーと設計ツールによって、概念設計からプロトタイプ作製までの時間を最短で数分に短縮できる。

システムの高性能化でエンジニアの作業負荷が増加

PLD(プログラマブルロジックデバイス)はその名の通りプログラム可能なロジックデバイスで、ICチップを製造した後でも内部の論理回路を定義したり変更したりできる。当初は回路ブロック間を接続するためのロジック回路(グルーロジック)などの用途に利用されてきた。必要な回路を複数個のディスクリートデバイスで構成するよりも実装基板を削減できるからだ。オペアンプやコンパレーターなどのアナログ回路ブロックを搭載したPLDも登場した。

ロジック回路の大規模化や高性能化の要求も高まり、CPLDやFPGAが登場した。これらは単なるユーザーロジックの領域拡大にとどまらず、大規模な機能ブロックをハードマクロとして取り込める。半導体プロセスの微細化とともに、性能や機能の面でFPGAは大きく進化している。こうした技術革新によって広義のPLD市場は一気に拡大した。

その分、ICチップに集積されるロジック回路の規模は格段に大きくなり、複雑化した。消費する電力やパッケージサイズも大きくなった。設計エンジニアは論理回路設計に用いる「VHDL」や「Verilog HDL」といったハードウェア記述言語を理解しなければならず、プログラミングの専門知識も必要になった。この結果、設計エンジニアの作業負荷が一気に増え、新製品を市場投入するまでの期間を短縮するのも極めて厳しくなりつつある。

概念設計からプロトタイプ作製までを分単位で実行

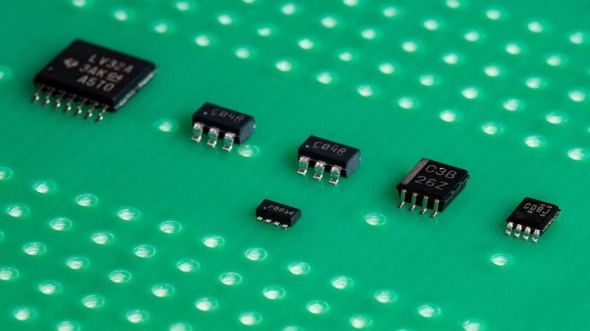

Texas Instruments(TI)は長年積み上げてきたロジック製品での強みを生かし、需要が拡大する比較的小規模のPLD「TPLDファミリー」を発表した。同社がPLDを市場投入するのは初めてとなる。その背景には、システム設計において小型化や軽量化、高密度実装への要求が強まってきたことがある。設計エンジニアの間では、「設計の複雑さを軽減したい」「搭載する基板での占有面積を削減したい」「サプライチェーンを簡素化したい」「開発期間を短縮したい」といった声が一段と高まってきた。これらを達成するため、手軽にカスタマイズできるPLDが注目されている。

TIのPLD事業のターゲットは、FPGAのように集積されるロジック素子が数千以上にも及ぶ大規模な回路を必要とする用途ではない。「電気自動車(EV)やサーバなどの分野でも、機器の小型化や低消費電力化のために小規模PLDのニーズは高まっている」(TI)

こうした分野でロジック設計のエンジニアが直面している主な課題は3つある。「基板上の限られたスペースに、より多くの機能を実装すること」「複雑化するプログラミングの専門知識が必要なこと」「車載や産業用途向けのパッケージオプションや仕様が限られていること」だ。

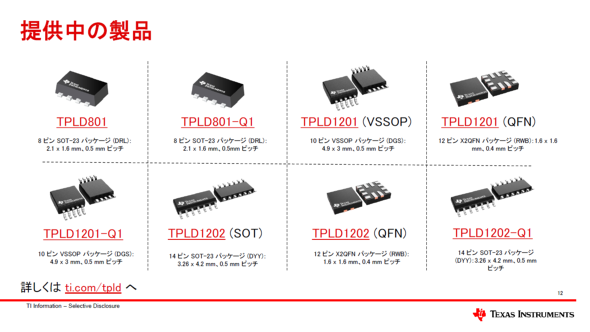

これらの課題を解決するために開発されたのがTPLDファミリーだ。今回発表したのは8製品で、4種類の業界標準パッケージを採用している。0.5mmピッチの8端子SOT-23を用いた「TPLD801」と「TPLD801-Q1」は外形寸法が2.1×1.6mmと小さく、はんだ付け実装が可能だ。

「TPLD1201」と「TPLD1201-Q1」は0.5mmピッチの10端子VSSOP、「TPLD1202」と「TPLD1202-Q1」は0.5mmピッチの14端子SOT-23を採用。「TPLD1201」と「TPLD1202」は、外形寸法が1.6×1.6mmと極めて小さい0.4mmピッチの12端子QFNだ。

実装面積を最大94%削減、BOMも80%減に

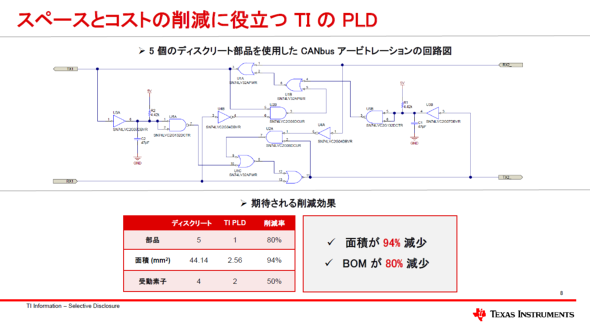

これらの新製品はコンビネーションロジックやシーケンシャルロジック、アナログブロックなど最大で40個の素子を単一チップに内蔵している。これにより、複数個のディスクリート部品で設計した回路よりも実装面積を大幅に削減できる。1個のPLDに回路を集積できれば部品点数(BOM)を減らせるのでコスト削減にもつながる。

省スペース化とコスト削減の一例として、TIはCANbusアビトレーション回路を挙げた。これまでのようにディスクリート部品を用いると回路の構成に5〜6個が必要で、実装面積は44.14mm2になる。TPLD1201を使えば1個で済み、実装面積も2.56mm2と極めて小さい。占有面積で94%減、BOMでは80%減となり、いずれも大幅な削減効果が期待できる。

省電力で動作温度範囲が広い

TIのPLDは消費電力も少なく、静止電流は1μA未満だ。つまり、EVや電動工具、バッテリーパック、ゲーム用コントローラといった用途においてバッテリーの使用時間をこれまでよりも長くできる。動作温度範囲も−40〜125℃と広いため、バッテリー管理などの用途に適している。車載用半導体の信頼性試験規格である「AEC Q-100」の認証も取得済みだ。

TIのPLDは、全製品で汎用(はんよう)入出力やルックアップテーブル、デジタルフリップフロップ、パイプディレイ、フィルター、RC発振器をサポートしている。TPLD1201とTPLD1202は、選択可能な内部電圧リファレンスオプションやヒステリシス機能を搭載したアナログコンパレーターなどのアナログ機能も統合している。TPLD1202はSPIやI2C、ウォッチドッグタイマー、ステートマシンといった機能も搭載している。

コーディング不要で設計時間を大幅短縮

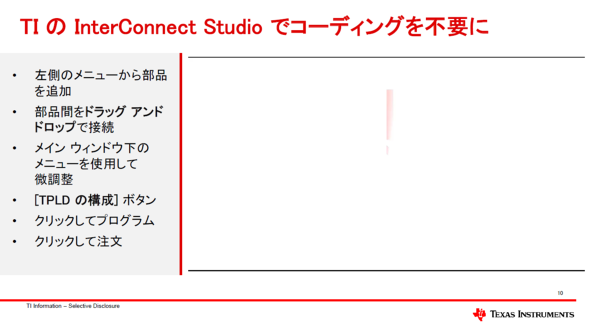

ICを設計するエンジニアにとって、設計の複雑さの軽減は重要だ。こうした設計エンジニアの悩みを解決するため、TIは設計ツール「InterConnect Studio」を無償で提供する。InterConnect Studioはドラッグ&ドロップ形式のGUIや統合型のシミュレーション機能を備えている。これらの機能を活用すればコーディング作業が不要になる。

この結果、ソフトウェアコーディングの経験がないエンジニアでもロジック回路の作成やロジック素子パラメーターの微調整、エラーチェック、消費電力の推定値表示などを比較的容易に行える。組み込みのシミュレーターをさまざまなプローブポイントで動作させれば、設計した回路の特性が期待値を満たしているかどうかを速やかに確認できる。

しかも、デバイスの設計から動作検証、PLDへの書き込みまで、わずか数分で完了する。設計の複雑さや設計者の経験値にもよるが、熟練のエンジニアでもPLDへの書き込みまでは通常30分以上かかる。それを数分のレベルに短縮できる。さらに重要なのは、設計エンジニアがハードウェア記述言語を新たに勉強しなくて済むということだ。

InterConnect Studioの「直接注文機能」を利用すれば、カスタムサンプルや量産デバイスをTIのサイトで直接注文できる。プログラム済みのPLDを入手できるので、応用機器を市場に投入するまでの期間を大幅に短縮することが可能だ。

新製品は2024年12月に量産を開始する。1000個購入時の参考単価はTPLD801が0.19米ドル、TPLD1202-Q1は0.52米ドル。InterConnect Studioは既に公開されており、TI.comで無償ダウンロードできる。評価基板「TPLD1201-DGS-EVM」は69米ドルで、TI.comで購入できる。USBプログラマー(書き込みツール)は59米ドルとなっている。

TIは、PLDの採用を検討しているユーザーに技術記事や評価基板、製品データシートなど、さまざまな関連情報を提供してユーザーのシステム開発を支援する。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ合同会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2024年12月18日