高電圧大電流のバッテリー遮断スイッチになぜSiCが最適なのか、Microchipが徹底考察:利点を最大限に生かす設計上の考慮点は

単相や三相の系統電力またはエネルギー貯蔵システム(ESS)を電源とする、DCバス電圧が400V以上の電気システムは、ソリッドステート回路保護によって、信頼性と回復力を向上できる。本記事では、Microchip TechnologyのSiC事業部 シニア テクニカルスタッフ アプリケーションエンジニアを務めるEhab Tarmoom氏が、高電圧、大電流のバッテリーディスコネクトスイッチにおけるSiC技術導入やパッケージング技術のもたらす利点および、システムの寄生インダクタンスと過電流保護限界の特性評価の重要性などについて考察する。

単相や三相の系統電力またはエネルギー貯蔵システム(ESS)を電源とする、DCバス電圧が400V以上の電気システムは、ソリッドステート回路保護によって、信頼性と回復力を向上できる。高電圧ソリッドステート ディスコネクトスイッチでは、設計上で考慮すべき決定事項として半導体技術、デバイスの種類、熱パッケージング、デバイスの耐久性、回路遮断時の誘導エネルギーの管理などが挙げられる。

本記事では、高電圧、大電流のバッテリーディスコネクトスイッチにおけるパワー半導体技術の選択や、半導体パッケージの定義における設計上の考慮点、システムの寄生インダクタンスと過電流保護限界の特性評価の重要性について考察する。

ワイドバンドギャップ半導体技術の優位性

最適な半導体材料を選択する際には、いくつかの特性を考慮する必要がある。その目標は、最小のオン抵抗、最小のオフリーク電流、高い電圧遮断能力、高い電力能力を持つスイッチだ。

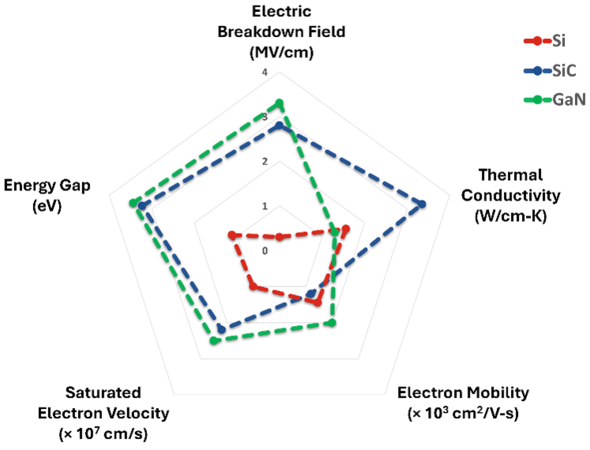

図1に、Si(シリコン)、SiC(炭化ケイ素)、GaN(窒化ガリウム)の半導体材料特性を示す。SiCとGaNの絶縁破壊電界は、Siの約10倍で、ドリフト領域の厚さは絶縁破壊電界に反比例するので、同格のSiデバイスの10分の1の厚さで設計できる。さらに、ドリフト領域の抵抗は絶縁破壊電界の3乗に反比例する。この結果、ドリフト領域の抵抗は1000倍近く低くなる。全ての損失が伝導損失である固体スイッチアプリケーションでは、高い絶縁破壊電界は大きな利点だ。この抵抗の減少によって、ダイナミックラッチアップの問題も解消される。

SiやGaNの3倍というSiCの熱伝導率は、チップの冷却と熱設計の簡素化を可能にする。また、同等のターゲット接合温度であれば、より高い電流動作が可能になる。より高い熱伝導率は、高い絶縁破壊電界と相まって、低いオン抵抗となり、熱設計をさらに単純化する。

ワイドバンドギャップ(WBG)半導体材料であるSiCは、Siの約3倍のエネルギーギャップを持ち、より高温での動作が可能だ。SiCは、自由電荷キャリアの濃度が低くSiよりも数百度高い温度で動作可能だが、現在の技術に基づくその他の要因(パッケージング、ゲート酸化膜リークなど)により、デバイスの最大連続接合温度は175℃に制限される。WBG技術のもう1つの利点は、オフ状態のリーク電流が少ないことだ。

これらの特性を考慮すると、SiCはこのアプリケーションに最適な半導体材料だ。

デバイスタイプの違い:IGBT、MOSFET、JFET

トランジスタの種類も重要な要素だ。システムの熱要件を満たすためには、伝導損失を最小限に抑える必要がある。また、軽負荷状態を含む全ての動作ポイントで効率を最大化するために、電圧降下も最小限に抑える必要がある。これはバッテリー駆動システムでは特に重要で、DCシステムを含む多くのシステムにおけるもう1つの重要な要素は、双方向の電流の流れだ。

一般に、伝導損失が低く、電圧降下が小さく、逆伝導能力を持つトランジスタが望まれ、考慮されるトランジスタは、IGBT、MOSFET、JFETだ。

IGBTはピーク負荷電流ではMOSFETと同等の伝導損失だが、負荷電流が減少すると、IGBTベースの製品の効率は低下する。これは、電圧降下がコレクタ電流に依存しないほぼ一定の電圧降下と、コレクタ電流に比例する電圧降下の2つの要素で構成されるためだ。MOSFETの場合、電圧降下はソース電流に比例する。MOSFETにはIGBTのようなオーバーヘッドがないため、軽負荷状態を含む全ての動作点で高効率を実現できる。

MOSFETは、第1象限と第3象限でチャンネル伝導が可能で、順方向と逆方向に電流を流すことが可能だ。MOSFETの第3象限動作の付加的な利点は、一般に第1象限よりもオン状態の抵抗がわずかに低いことだ。一方、IGBTは第1象限でのみ電流を伝導し、逆電流伝導には逆並列ダイオードが必要になる。

JFETは、順方向伝導と逆方向伝導の両方で動作し、MOSFETと同様にドレイン電流に比例した電圧降下を持つ。MOSFETと異なる点は、JFETが空乏モードデバイスであることだ。つまり、JFETは通常オンであり、電流の流れを抑制するためにゲートバイアスを必要とする。これは、システムの故障状態を考慮する際に、設計者にとって課題になる。回避策として、直列低電圧Si MOSFETを含むカスコード構成を使用して、ノーマリーオフデバイスを実現できるが、この場合複雑さが増し、大電流アプリケーションにおけるJFETの利点の一部が損なわれる。

ノーマリーオフデバイスであるSiC MOSFETは、多くのシステムで必要とされる低抵抗と制御性を兼ね備えている。

サーマルパッケージング

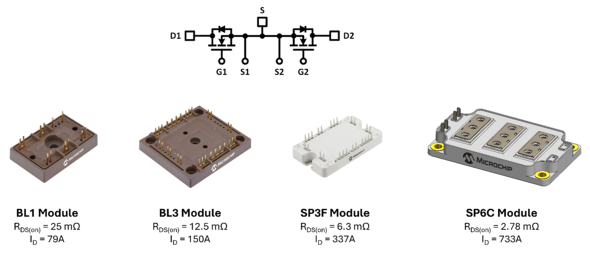

SiCパワーモジュールは、ディスクリートMOSFETの並列接続では実現が困難な高レベルのシステム最適化を可能にする。Microchip社の「mSiC」モジュールは、幅広い構成と電圧/電流定格で提供されている。その中でもコモンソース構成は、2つのSiC MOSFETを反直列構成で接続し、双方向の電圧/電流ブロッキングを可能にする。各MOSFETは、定格電流と低いオン抵抗値を実現するために、複数チップを並列に接続して構成されている。一方向バッテリーディスコネクトスイッチの場合、2つのMOSFETはパワーモジュールの外部に並列接続される。

チップを低温に保つためには、低いオン抵抗と低い熱抵抗が必要だ。モジュール内で使用される材料は、接合部からケースまでの熱抵抗とその信頼性を決定する重要な要素となる。具体的には、ダイアタッチ、基板、ベースプレートの材料特性が、モジュールの熱抵抗に大きく関係する。高い熱伝導率を示す材料を選択することで、熱抵抗と接合部温度を最小限に抑えられる。熱性能に加えて、熱膨張係数(CTE)が密接に一致する材料を選択することで、材料の界面と内部の両方における熱応力を低減し、モジュールの寿命を延長できる。表1は、これらの熱特性をまとめたものだ。AlN基板とCuベースプレートは、mSiCパワーモジュールの標準だ。Si3N4基板とAlSiCベースプレートによるオプションでは、より高い信頼性が実現できる。図2では、標準SP3FおよびSP6Cパッケージのコモンソースパワーモジュールと、DO-160に適合した高信頼性ベースプレートレスBL1およびBL3パッケージを示している。

| 材料 | 熱膨張係数(CTE) (ppm/K) |

熱伝導率 (W/cm-K) |

密度 (g/cm3) |

|

|---|---|---|---|---|

| ダイ | Si | 4 | 136 | |

| SiC | 2.6 | 270 | ||

| 基板 | Al2O3 | 7 | 25 | |

| AlN | 5 | 170 | ||

| Si3N4 | 3 | 60 | ||

| ベースプレート | CuW | 6.5 | 190 | 17 |

| AlSiC | 7 | 170 | 2.9 | |

| Cu | 17 | 390 | 8.9 | |

| 表1:ダイ、基板、ベースプレートの熱特性 | ||||

デバイスの堅牢性とシステムのインダクタンス

回路遮断装置におけるもう1つの設計上の考慮点は、高い誘導エネルギーだ。リレーとコンタクターのサイクル数には限りがある。これらは一般的に、無負荷の機械的なスイッチングサイクルで指定され、電気的に負荷のかかるスイッチングサイクルは大幅に少なくなる。システム内のインダクタンスは、電流を遮断する際に接点を横切るアーク放電を引き起こし、劣化の原因となる。そのため、電気サイクル定格の動作条件は具体的に定義され、寿命に強く影響する。

それでも、コンタクターまたはリレーを使用するシステムでは、高短絡電流が流れると接点が溶着して閉じることがあるため、上流のヒューズが必要だ。ソリッドステート ディスコネクトスイッチは、このような劣化に悩まされることがなく、より信頼性の高いシステムを実現できる。とはいえ、大電流を遮断する際に存在する誘導エネルギーを管理するには、システムの寄生インダクタンスと負荷インダクタンスおよび、キャパシタンスを理解することも不可欠だ。

誘導エネルギーはインダクタンスに比例し、遮断時のシステムの電流の2乗に比例する。スイッチの出力端子で短絡が発生すると、電流が急速に増加し、バッテリー電圧とソースインダクタンスの比の割合で上昇する。SiCパワーモジュールをアバランシェモードで動作させることは推奨されないため、この誘導エネルギーを吸収してモジュールを保護するスナバ回路またはクランプ回路が必要となる。しかし、沿面距離とクリアランスの要件を満たすように適切に設計された場合、スナバ回路に導入される寄生が、その有効性をさらに制限する。従って、モジュールの内部インダクタンスによる電圧オーバーストレスと電流の急激な減少を制限するために、スイッチは十分にゆっくりとオフになる必要がある。低インダクタンスに設計されたモジュールは、この電圧ストレスをさらに最小化するのに役立つ。

Siパワーデバイスでは、大電流を高速に遮断すると、寄生NPNやサイリスタがトリガーされるリスクが生じ、制御不能なラッチアップが発生し、最終的に故障に至る。またSiCデバイスでは、非常に高速なターンオフにより、スナバやクランプが高エネルギーを吸収するまで各チップがターンオフし、低エネルギーのアバランシェ破壊が発生する可能性がある。

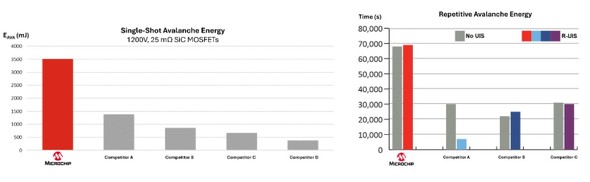

Microchip社のmSiC MOSFETは、アンクランプ誘導スイッチング(UIS)用に設計およびテストされていて、スナバやクランプが劣化し始めたときに追加の安全マージンを提供する。図3は、市場の他のSiCデバイスと比較したシングルショットおよび繰り返しのUIS性能を示している。

デバイスレベルでの短絡能力では、IGBTの方が優れているが、実際のシステムではまた異なったストレス条件にさらされる。システムインダクタンスの固有の電流制限動作により、モジュールがその短絡電流定格に達することはまずない。制限要因は、スナバまたはクランプ回路の設計だ。コスト効率の良いコンパクトなスナバを設計するには、システムレベルの許容ピーク短絡電流は、モジュールの短絡電流定格を大幅に下回る値に制限される。

例えば、9個の並列チップで構成され、短絡電流が1350Aを超えないように設計された500Aのバッテリーディスコネクトスイッチでは、電流分布が均一であると仮定した場合、各チップは150Aの電流を流す。これは、試験期間中、電流が数百アンペアを超えるデバイスレベルの短絡試験よりもはるかに低い電流だ。電圧クランプデバイスの最適化は、堅牢なソリッドステート ディスコネクトスイッチの設計において重要な部分だ。

その他の設計上の注意点

パワーデバイス以外にも、電流検出技術、過電流検出と保護、機能安全など、制御電子機器に関連する設計上の注意点がある。電流センシングにシャント抵抗器を使用するか磁気技術を使用するかの決定は、高速応答が不可欠な低寄生インダクタンスのシステムにおける設計にとって重要だ。過電流検出にハードウェアまたはソフトウェア、あるいは2つを組み合わせて使用するかも、機能安全要件を満たすように設計する場合には特に重要な決定事項だ。

ここまでソリッドステート ディスコネクトスイッチにおける高電圧パワーデバイスの選択と設計におけるいくつかの重要な側面について考察してきた。SiCとパッケージングの特長によって従来の機械的な遮断スイッチに比べ、ソリッドステート ディスコネクトスイッチはシステムレベルで利点を持つ。SiC技術を使用することで、多くのシステムで必要とされる低導通損失を実現する低オン抵抗と熱抵抗のデバイスが入手可能になり、同時に高信頼性を保証する材料も使用できるようになった。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

提供:マイクロチップ・テクノロジー・ジャパン株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2024年12月27日