次世代プロセッサはダイナミックな電圧制御と並列処理手法が決め手:スプリング・マイクロプロセッサフォーラム・ジャパン2006から(2/3 ページ)

消費電力を上げずに性能を上げるマイクロプロセッサが回路とアーキテクチャの2つの工夫で実現できる。回路的には動作状態に応じて電源電圧と基板バイアスをダイナミックに変える方法が主流になりそうだ。アーキテクチャ上はこれまでのメインフレームの実現に使われてきた各種の並列処理技術をプロセッサに応用するようになってきた。スプリング・マイクロプロセッサフォーラム・ジャパン2006では、このような方向がはっきり見えてきた。

デジタル的に電圧を可変

米Freescale Semiconductor社もリーク電流による消費電力の増大を抑えるため、ダイナミックな電圧制御法を使う。基板バイアスをウエルに加えたり、デュアルのVthを使う。もちろん、未使用ロジック部の電源の遮断といった工夫も盛り込まれる。また、後述する「MSC8144」では、チップ内に3つのクロックドメインを設定することができ、低速動作で構わないブロックには低い周波数を割り当てることが可能になっている。

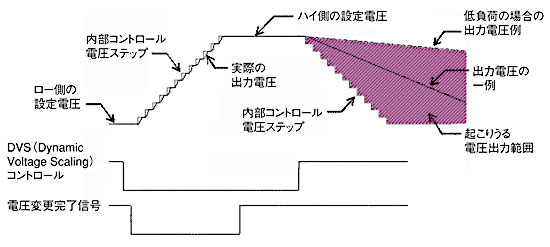

電圧を変える場合には25mVステップで、例えば「MC13783」チップでは0.9Vから1.65Vまでデジタル的に制御する(図2)。SPIインターフェースを通じ設定するが、その設定時間を4/8/16μsで選択できる。

米National Semiconductor社は、ダイナミック電圧制御技術をさらに押し進め、適応型電圧制御技術を開発した。これは、チップ上に電圧と温度のセンサーを置き、電力を消費して温度が上がると自動的に電圧を下げようというもの。

同社が手がけてきたこれまでの適応型パワーマネジメント技術では温度センサーにより動作周波数を下げるように制御してきたが、今回の適応型電圧制御技術では動作時も静止時も消費電力が多いときには動作周波数だけではなく、電圧も下げる。最大70%の削減が可能だ。

デジタル的にステップごとに電圧を変える。フィンランドにある同社のポータブルパワーシステムズのシステムアプリケーションマネジャーであるJuha Pennanen氏によると、IPコアとしてライセンスするビジネスを展開する予定だという。

さまざまな並列処理技術を駆使

並列処理アーキテクチャでは、SIMD (single instruction multiple data)やVLIW(very long instruction word)、マルチスレッド、マルチコア、パイプラインなどの大型コンピュータで使われていた技術に加え、数十個以上の小型プロセッサを並列動作させる超並列演算手法も消費電力を上げずに性能を上げる有力な手段として生まれ変わった。

SIMD+VLIW+マルチコア

富士通研究所は、メディアプロセッサコア「FR550」を2個内蔵したマルチコアプロセッサ「FR577」を開発した。FR577は動作周波数320MHzで、MPEG2のSD映像3ストリーム、QVGA映像2ストリームを同時にデコードできる処理性能を持ち、消費電力は700mWに抑えた。

プロセッサコアは命令レベルの並列性をVLIW方式、データレベルの並列性をSIMD方式で行い、加えて複数のコアを組み合わせる。

同社は今回、消費電力に対する各並列性の効果を実証し報告した。例えばSIMD方式の場合、1命令で1演算処理するときの消費電力は400mWとなるが、1命令4演算同時処理するときは約100mWで、電力効率は4倍となる。消費電力はクロックやバス系統が支配的で、演算器を増やしてもそれによる消費電力の増分は少ない。

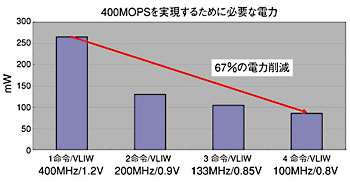

VLIW並列性についても消費電力への効果を検証した。400MOPSの性能を得るために、プロセッサコアへの印加電圧を1.2Vに固定し、命令数と動作周波数の関係を調べた。1命令実行だと動作周波数は400MHzとなり、消費電力は250mWを超えた。これを4命令実行に増やすと動作周波数は100MHzで済み、消費電力は200mW以下となり、1命令実行に比べ27%削減できる。さらに、4命令実行だと電源電圧を0.8Vまで下げても400MOPSの性能を達成でき、総合すると67%の電力を削減できることが分かった(図3)。

システムLSI開発研究所プロセッサソリューション開発部の部長を務める須賀敦浩氏はSIMD方式とVLIW方式を組み合わせたときの電力効率にも言及し、「FRプロセッサは16演算並列処理時に1演算処理時の20%の電力で1演算実行できる」と述べた。

富士通研究所は、1コアとマルチコアにおける消費電力・性能比も検証した。これによると4コアの場合、1コアに比べて性能は3.2倍となり、消費電力は2.2倍にとどまることが分かった。

こうした実証をベースに同社では、すでにFR550コアを4個実装したマルチコアプロセッサ「FR1000」などを開発してきたが、FR550コアを2個実装したFR577も新たに開発した。FR577は動作周波数440MHzで、ピーク性能は3520MIPS/3.52GFLOPS/21.22GOPSを達成している。消費電力は1W(320MHz動作時は700mW)と小さい。

リアルタイムプロセッサを狙う

英ARM社の新しいリアルタイムプロセッサ用コア「Cortex-R4」は組み込みシステム向けに、割り込み応答時間の短縮や用途に応じた機能構成を柔軟に行えるなどの特徴を持つ。Cortex-R4は、2004年10月に発表したCortex-M3、2005年10月発表のCortex-A8に続く、ARMv7アーキテクチャの第3弾。速度の遅いRAMを使えるため消費電力を抑えることができる。

従来のARM11コアと同様Cortexプロセッサが採用した8段パイプラインのうち、フェッチステージを従来の1段から2段に増やすことで、低速のメモリーを使えるようにした。また、プリデコードが2つあるため、命令ストリームを分解してThumb-2コードの命令サイズの特定や、プリディケイデッド命令ブロックの前処理が行える。このため、その後のデコードが簡単になる。

実行部はデータのアクセスで2段のパイプラインを使っており、キャッシュとTCMにはアクセスタイムがさほど速くなく、消費電力の小さい安価なメモリーを使うことができる。例えば、動作周波数が400MHzのCortex-R4に必要なRAMのアクセスタイムは2.5ns以下であればよい。これに対し300MHz動作のARM946E-Sでは1.3ns以下が必要となる。Artisanのメモリーコンパイラで16KバイトのRAMをそれぞれ設計したとき、Cortex-R4用がARM 946E-S用に比べ消費電力で53%、リーク電流で80%、チップ面積で35%それぞれ小さくなるという(アームでエンジニアリンググループ エンベデッドシステムのアシスタントマネジャーを務める田辺洋吾氏)。

Cortex-R4をTSMC社の90Gプロセスで製造した場合、8Kバイトキャッシュ付きでチップ面積は1.43mm2と小さく、電力効率は0.4mW/MHz以下で、1.60DMIPS/MHzを達成している。動作周波数は273MHzだが高速ライブラリを使うと400MHz以上での動作も可能である。

スーパースケーラで性能向上

TI社のF1プロセッサ(Cortex-A8コア)の開発では、性能の向上を目標とした。日本テキサス・インスツルメンツの我孫子茂志氏は「F1プロセッサは65nmプロセス技術でGHz動作が可能なアーキテクチャ」という。性能向上のために、1クロック当たりの命令実行数(IPC)を改善した。2命令同時発行のスーパースケーラ技術を使った初めてのARMコアとなる。L2キャッシュメモリーも今回内蔵した。

なお、65nm低消費電力プロセス技術において配線層は6層(6層目は電源とクロック専用)とし、製造コストを抑えている。消費電力に影響を与えるリーク電流は0.3nA/μmと小さい。

Copyright © ITmedia, Inc. All Rights Reserved.