オペアンプ設計の要諦をつかむ(2/5 ページ)

オペアンプの設計では、用途に応じてさまざまな特性を実現しなければならない。しかし、何を目標とするかにかかわらず、共通に留意すべき事柄もいくつかある。本稿では、そうしたポイントをピックアップし、設計を進める上で指針となる「考え方」を提示する。

最も重要なのは「安定性」

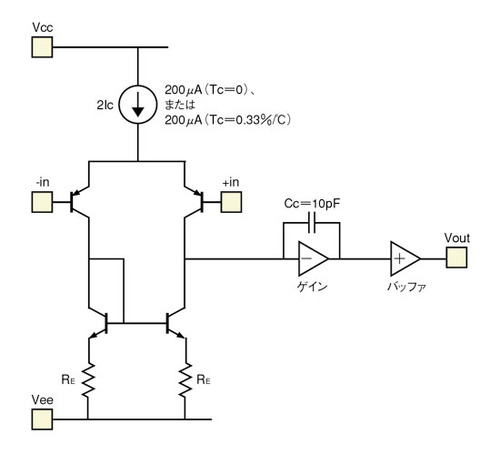

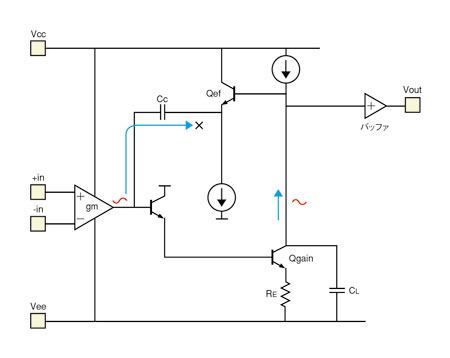

オペアンプの設計において、一番に考えなければならないことは安定性である。設計目標となるパラメータの実現はもちろんだが、何よりも「発振しない」ということが重要だ。当たり前のことではあるが、実は最も失敗しやすいポイントでもある。ここでは、図1に示すような差動入力段とゲイン段を含む回路の安定性について考えてみる。

・差動入力段の温度特性の補正

一般に、「バイポーラトランジスタは低温で発振しやすい」といわれる。その理由は、発振条件を決めるバイポーラトランジスタのトランスコンダクタンスgmが、コレクタ電流Icに比例し、絶対温度Tに反比例するからだ(以下参照)。

ここで、kはボルツマン定数、qは電子の電荷である。この式から、Icが一定ならば、低温でgmが大きくなることが分かる。例えば温度Tが−50℃(223K)の場合と150℃(423K)の場合とでは、gmの値にほぼ2倍の差が出る。これは、トランジスタ単体であっても差動入力段であっても同じことである。従って、位相補償はワーストケース、つまり低温のときに安定になるように行わなければならない。しかし、そうなると室温/高温での帯域幅を犠牲にせざるを得ない。

図中の差動入力段のテール電流(差動入力段のエミッタ共通電流)2Icに温度に対して正の係数を持たせれば、温度にかかわらずgmを一定に保つことができ、位相補償が行いやすくなる。その半面、図1に示すようなオペアンプの場合、位相補償容量Ccが一定だとすれば、そのスルーレートSRは、2Icの値に依存するので当然のことながら温度依存性を持つことになる。しかし通常は、SRの温度依存性よりも、安定性のほうがはるかに重要である。

差動入力段のテール電流2Icが200μA、温度が300Kであるとすれば、図中の差動入力段のgmは以下の値となる。

この値から300K付近でのgmの温度係数Tcが以下のようにして求まる。

さらに直感的に分かりやすくするために、300K付近でのgmの温度係数Tcをパーセント表示にすると以下のようになる。

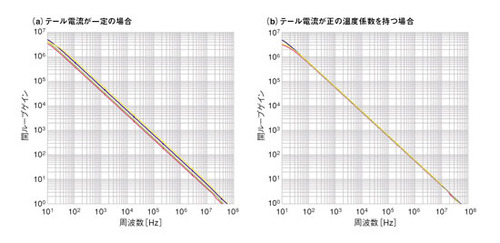

従って、テール電流2Icの温度係数を+0.33%/℃とすれば、ゲイン帯域幅を一定に保つことができる。2Icが温度係数を持たない場合と正の温度係数を持たせた場合のシミュレーション結果からこのことを確認してみたい(図2)。

図2(a)は、テール電流2Icが一定である場合の結果を表している。この場合、ゲイン帯域幅積GBWPは以下のようになる。

このように、ゲイン帯域幅積の温度依存性は明らかである。一方、図2(b)は、2Icに正の温度係数を持たせた場合の結果を表している。この場合、ゲイン帯域幅積は温度にかかわらず一定である(以下参照)。

これにより、位相補償において、第2ポールによる過剰な位相遅れ(excess phase lag)について考慮する際、メインループの周波数特性が温度によって変わらないため設計が容易になる。

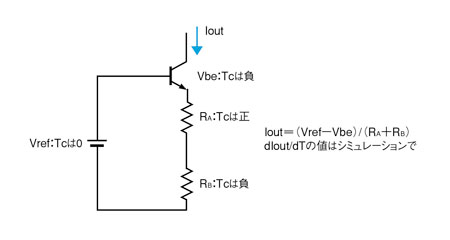

なお、所望の温度係数を持つ電流源の設計方法はいろいろあるが、基本的には温度に比例する項を持つ何か(電圧、電流、抵抗など)と温度に反比例する項を持つ何かがあればその組み合わせによって実現することができる。例えば、図3に示すような電流源で抵抗RAが正の温度係数を持ち抵抗RBが負の温度係数を持つならば、この電流源の温度係数は、それそれの温度係数とベース‐エミッタ間電圧Vbeの温度係数(負の温度係数)を混合したものとなる。具体的な値の算出はシミュレーションによって行えばよい。いずれにしても、RAとRBの値で定電流Ioutの温度係数Tcはいかようにも設定できる。

・ゲイン段の構成

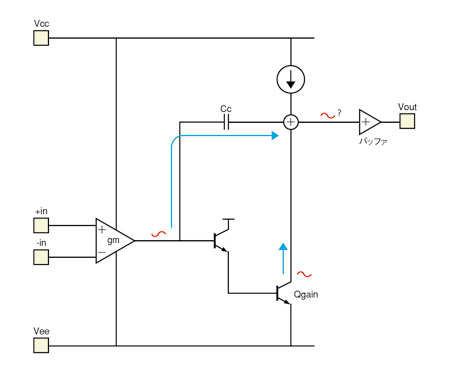

次にゲイン段に関する留意点について触れておく。図4に、一般的なゲイン段の構成を示す。

ゲイン段では、その増幅量と位相が問題となる。ゲイン段による第2ポールは安定性を阻害するので注意が必要だ。周波数が高くなればなるほど、ゲイン段の出力の位相は予想しにくくなる。なぜならゲイントランジスタQgainのベース‐コレクタ間接合容量Cjcと位相補償容量Ccによる信号パスによって位相が乱されるからである。またゲイン帯域幅を広げると、ゲインが0dBになる周波数foがゲイン段によって生じる第2ポールに近づいてくるため、過剰な位相遅れが生じる。それらの重ね合わせとして全体の位相が決まるため、実際の位相が分かりにくくなってしまうわけだ。

またゲインを大きくとるためにゲイントランジスタQgainのバイアス電流を上げてgmを稼ぐと、思わぬピークが出来てリンギングが生じたり、最悪の場合、ローカル発振に至って外部回路ではそれ止めることができなくなったりする。

これらの不安定要因についての解析は複雑なものになる。最も有効なのは、コンピュータシミュレーションによる方法だ*3)。

図5に示したのは、ゲイン段で生じる問題への対処を施した回路図である。Cjcによる影響は取り除けないが、Ccによる信号パスの影響はエミッタフォロア(図5のトランジスタQef)を追加して信号パスを遮断することで解決できる。ただし、その場合には、エミッタフォロアの交流エミッタ抵抗re(トランジスタにおける交流等価抵抗)によってゼロが新たに出来るので注意が必要だ。またgmを上げることによるピーキングを軽減するために、明示的にCLを付加して高域をロールオフさせるというのも手である。さらに、ゲイントランジスタQgainによるゲイン段のgmの上限を決めるために、エミッタ抵抗RE(直流外部抵抗)を加える方法も有効だ。

脚注

※3…James E. Solomon, The Monolithic Operational Amplifier: A Tutorial Study, December 1974

Copyright © ITmedia, Inc. All Rights Reserved.