オペアンプ設計の要諦をつかむ(3/5 ページ)

オペアンプの設計では、用途に応じてさまざまな特性を実現しなければならない。しかし、何を目標とするかにかかわらず、共通に留意すべき事柄もいくつかある。本稿では、そうしたポイントをピックアップし、設計を進める上で指針となる「考え方」を提示する。

ノイズの低減策

前節ではオペアンプの最重要項目として安定性を取り上げた。もう1つ、オペアンプに要求される性能の中で重要なものとしてノイズ性能が挙げられる。ノイズが大きいと、そのオペアンプを適用できるアプリケーションの種類に制限が加わることになる。またノイズはほかの性能を覆い隠してしまう要因となる。そのため、ノイズのレベルは重要な設計パラメータなのである。ここでは、ノイズの評価を試みるために単純化したオペアンプの回路図として再び図1を用いることにする。なお、フリッカノイズについてはプロセス依存性があるので本稿では扱わないこととする。

低ノイズ設計においては、まず目標とするノイズレベルを設定する必要がある。バイポーラトランジスタのノイズの評価には、以下に列挙する各式が非常に有効である。

まず、抵抗Rが発生する熱雑音v2は以下の式で表される。

一方、バイポーラトランジスタの等価雑音抵抗Reqはベースの内部抵抗をrbとすれば、以下のようになる。

従って、バイポーラトランジスタが発生するノイズの周波数特性は以下に示すどちらかの式で表される(ここでgm=qIc/kTである)。

これらの式の意味するところは、Icによるショットノイズもベース抵抗rbによる熱雑音も同様に扱えるということだ。

具体的な例を用いて、その値を求めてみよう。まず、rbが100ΩでIcが100μAのトランジスタの入力換算雑音抵抗は、温度が300Kの場合、以下のように計算できる。

↓

従って、そのトランジスタの発生するノイズは以下のようになる。

↓

ここまでに説明したのは単一のトランジスタの場合である。差動入力トランジスタ対のノイズは、個々の入力トランジスタのノイズをvi2とすると、以下のように表される。

↓

このノイズ性能はかなり良い値である。ここでさらにノイズを低減しようと思えば、rbを小さくするかgmを大きくするかの選択となる。

まずrbを小さくするための簡単な方法としては、トランジスタのサイズを大きくする方法か、数個のトランジスタを並列に接続する方法が考えられる。いずれにせよ、チップ面積の増加や浮遊容量の増加といったマイナス要因が伴うことになる。

一方、gmを大きくするにはIcを増やす以外に手はない。それには入力バイアス電流Ibの増加が伴う。さらにゲイン帯域幅積が増すことで安定性に対する考慮も必要になる。

ここで入力トランジスタのサイズを2倍にし(これは入力オフセット電圧の改善にもなる)、rbを半分の50Ωとした場合のノイズ量を計算してみよう(以下参照)。

上式から分かるように、2.4nV/√Hzのうち72%がIc由来のショットノイズで、28%がrb由来のノイズである。つまり、ほとんどのノイズはIcで決まることが分かる。言い換えれば、rbを下げるためにこれ以上入力トランジスタのサイズを大きくしてもあまりメリットがないということだ。

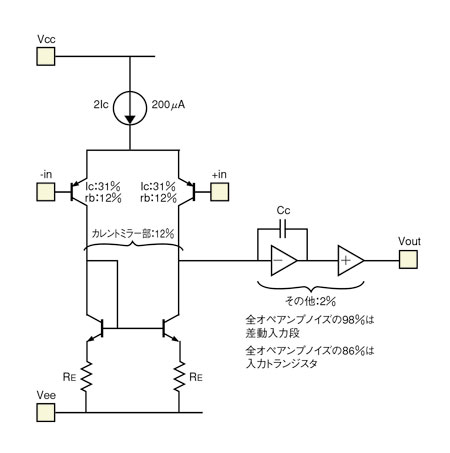

オペアンプ全体で見れば、入力トランジスタだけがノイズの発生源というわけではない。そこで、オペアンプの内部で、それぞれの素子がオペアンプ全体のノイズにどの程度の影響を与えるのかを確認してみる。図6は、オペアンプ全体のノイズシミュレーションを実行して個々の素子の寄与率を算出した結果である。この結果から、ノイズ全体の62%は入力トランジスタのIcに由来するショットノイズで、24%がrbに由来するノイズであることが分かる。また、全体のノイズの98%は差動入力段で決まり、入力トランジスタのペアが全体の86%を占める。

以上のことから、確かにノイズの発生源はオペアンプ内に散在しているが、全体の性能は、ほぼ入力トランジスタによって決まるといえる。

Copyright © ITmedia, Inc. All Rights Reserved.