低消費電力LSIの設計技術:最新技術動向をまとめて理解!(3/5 ページ)

携帯型端末などに用いるLSIには、当然のことながら、低消費電力化の実現が要求される。しかし、昨今では、それ以外の用途に向けたASICやSoCを設計する場合でも、低消費電力設計手法の適用が必須となっている。最新のプロセス技術を用いると、必然的にリーク電流が多くなってしまうからだ。本稿では、ASIC設計者が知っておくべき、消費電力の削減手法についてまとめる。

電圧スケーリングと並列化

別の低消費電力化手法に、Chinnery氏とKeutzer氏がその著書の中で解説している電圧スケーリングと並列化を利用する方法がある。Keutzer氏によると、これらは「最初は非実用的だと却下されていた手法だが、現在はかなり注目を浴びている」という。「性能を高めるために並列度を上げて、それらを低い電圧で動作させて消費電力を低減するのだ」とKeutzer氏は述べる。同氏はこの手法を以下のように説明する。

「ダイナミック消費電力は電圧の2乗に比例する。そのため、電圧を下げれば消費電力の削減に対して大きな効果が得られることは明らかだ。ではどのようにして電圧を低下させるのか。例えば実際のタイミング制約が2nsという場合に、まずはそれよりもタイミング制約を高く設定する。並列度を上げることで、クリティカルパスのタイミング制約を1.2nsにするといった具合だ。その上で電圧を低下させることにより、本来の目標値である2nsまで緩めていくのである。この手法によって面積は増加するが、それ以上に消費電力の面で大きな効果が得られる」。

クロックゲーティング

消費電力の削減に対しておそらく最も古くから利用されてきた手法がクロックゲーティングであろう。LSIのダイナミック消費電力の1/3から1/2は、チップのクロック分配回路で消費される。Keating氏は、「この技術の概念は非常に簡単だ。クロックが不要ならば、その供給を停止するというものだ」と語る。

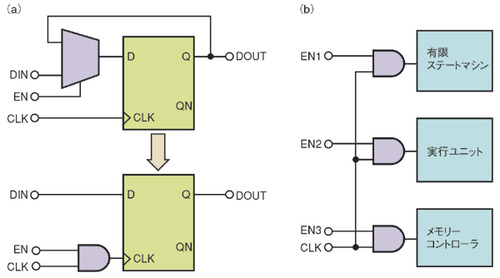

現在よく利用されているクロックゲーティング手法には、ローカルとグローバルの2種類がある(図4)。例えば、図4(a)の上のような回路であれば、常時クロックを必要としない。つまり、図4(a)の下のように、各フィードバックマルチプレクサをクロックゲーティングセル(AND回路)に置き換えることができる。そして、マルチプレクサを制御するイネーブル信号を用いて、クロックゲーティングセルの出力を制御すればよいのである。

従来、この置き換えは手作業で行われていたが、現在では市販の合成ツールで自動的に実施することができる。この作業のためのツールが自動的にマルチプレクサを検出し、フィードバック経路付きのマルチプレクサをクロックゲーティングセルに置き換えてくれるのだ。Keating氏は「32ビットのレジスタになると、この手法を用いることで大幅に電力を低減することができる」と語る。2007年のSNUG(Synopsys Users Group)において、米Intel社のエンジニアがこの手法によってダイナミック電力を43%削減したという例を発表している*2)。

もう1つのよく使用されるクロックゲーティング手法が図4(b)のグローバルクロックゲーティングである。通常、この手法ではクロックジェネレータモジュールから、単純にブロック全体のクロックを停止する制御を行う。ローカルクロックゲーティングとは異なり、ブロック全体の機能を停止させることになる。クロックツリー全体を停止することになるため、ローカルの場合に比べて、ダイナミック消費電力の削減量は大きい。

図4 ローカルクロックゲーティングとグローバルクロックゲーティングの概念図 (a)のローカルクロックゲーティングでは、データ信号(DIN)を受けるマルチプレクサにイネーブル信号(EN)を入力する代わりに、クロック信号(CLK)ラインにAND回路を挿入し、イネーブル信号を入力している。(b)のグローバルクロックゲーティングでは、それぞれのブロックにAND回路を挿入し、それにクロック信号を入力している。

省電力化メモリー

ダイナミック消費電力とリーク電力を低減するための別の手法として、メモリーの電力を削減することがよく行われる。メモリーの消費電力を削減する手法として最も簡単なのは、未使用のメモリーセグメントを停止することである。

これと同様の手法としては、メモリーの基板バイアス制御がある。未使用メモリーのトランジスタを逆バイアスすることにより、閾値電圧を上げてリーク電流を削減することで消費電力の低下を図る。

そのほかの手法として一般的なのは、省電力モードを備えたメモリーを用いることである。メインアプリケーションが動作してCPUがメモリーに対して読み出し/書き込みを行う際には、メモリーに大きな電力が供給される。省電力モード付きのメモリーは、データの読み書きが不要なときは、データの保存にだけ必要なレベルまで電圧を低下させる機能を備える。

脚注

※2…Pokhrel, Khem C, "Physical and Silicon Measures of Low Power Clock Gating Success: An Apple to Apple Case Study," proceedings of Synopsys Users Group, San Jose, CA, 2007.

Copyright © ITmedia, Inc. All Rights Reserved.