低消費電力LSIの設計技術:最新技術動向をまとめて理解!(4/5 ページ)

携帯型端末などに用いるLSIには、当然のことながら、低消費電力化の実現が要求される。しかし、昨今では、それ以外の用途に向けたASICやSoCを設計する場合でも、低消費電力設計手法の適用が必須となっている。最新のプロセス技術を用いると、必然的にリーク電流が多くなってしまうからだ。本稿では、ASIC設計者が知っておくべき、消費電力の削減手法についてまとめる。

パワーゲーティング

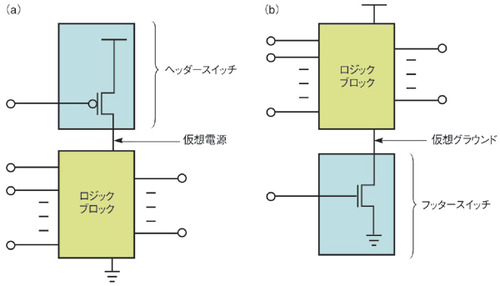

低消費電力設計において最も注目を浴びている手法は、おそらくパワーゲーティングだろう。パワーゲーティングでは、回路内の使用されていないブロックの電力を一時的に遮断する(図5)。これによりリーク電力の発生を防ぐ。

図5 パワーゲーティングの概念図 パワーゲーティングでは、パワーゲーティングトランジスタを、ロジックブロックの電源ラインやグラウンドラインに配置する。(a)は、電源ラインにパワーゲーティングトランジスタを配置した例で、(b)はグラウンドラインにパワーゲーティングトランジスタを配置した例である。

この処理は非常に複雑なものとなる。Keating氏はその問題点を以下のように指摘する。

「マルチ閾値電圧、マルチ電源電圧、クロックゲーティング、省電力メモリーなどについては、設計の下流を担当するだれかが考えてくれる。そのため、RTLを記述する設計者はこれらについて気にする必要がない。しかし、パワーゲーティングでは、RTLレベルでの考慮が必要となる。どのブロックをいつ遮断するのかということを把握してパワーコントローラを設計しなければならない。また、電源を遮断しないブロックの動作についても考慮しなければならない」。

従来からのパワーゲーティング手法としては、細粒度型(fine grained)と疎粒度型(coarse grained)の2つがある。細粒度型のパワーゲーティングでは、スイッチトランジスタをゲートのグラウンド側に配置する。これにより、一連の機能が使用されていないときにグラウンドへの接続を切断する。Keating氏によれば、「当初はライブラリ内のすべてのセルにこの手法を適用していた」という。しかし、「細粒度型のパワーゲーティングのほうが各セルの電力の特性評価が簡単であるため、従来はよく使用されていたが、この方法だとチップ面積が2〜4倍にもなる」(Keating氏)という深刻な問題があった。

パワーゲーティングを適用するセルとしないセルを組み合わせて設計することもできる。閾値電圧が高いセルはもともとリーク電力が少ないため、パワーゲーティングを用いる必要がない。

大抵の場合、パワーゲーティングではパワースイッチネットワークを使用した疎粒度型が用いられる。パワースイッチネットワークとは、ブロック全体をオン/オフする、並列に構成されたスイッチトランジスタの集まりのことだ。この手法では細粒度型の手法ほどチップ面積は大きくならないが、セルごとの特性評価はより困難になる。

Sequence Design社のFrenkil氏は、「中粒度型(medium grained)のパワーゲーティングという中間的な方法も出現しつつある」と語る。「この手法では、小さなブロックに個別に電力を供給する。高速性能に優れる65nmプロセスでは、リーク電力が総消費電力の40〜50%にも達する。このような高性能チップを設計する場合、リーク電力を削減するために、それぞれ別々に制御可能な電力ドメインを複数用意する。一般的なチップサイズのもので、20個の電力ドメインを持つチップが存在するし、最先端のチップでは100個以上の電力ドメインを持つものもある」(同氏)という。

Frenkil氏は、「すべての手法の中でパワーゲーティングが最も有望だ」と説いた。「パワーゲーティングを用いれば、リーク電力を大幅に削減可能だ。それに加え、基板バイアス制御などとは異なり、将来的にもその手法を適用できる」と同氏は述べる。

EDAベンダーらは、パワーゲーティング手法の適用を自動化しようと積極的に活動している。対立する低消費電力設計用の規格であるUPF(unified power format)とCPF(common power format)は、いずれもより効率的にパワーゲーティング手法を実装することを目標にしている。

Keating氏によれば、「UPFを用いる場合、RTLでパワーコントローラを設計しなければならないが、パワーメッシュ、アイソレーションセル、リテンションレジスタ回路への対応を支援するツールがいくつか存在する」と指摘する。同氏は「RTLの中で行う代わりに、UPFを用いて仕様を記述することによって、隔離された複数のブロックに対して低消費電力化を図ることができる。RTLでは何行にもわたって記述しなければならない処理がUPFでは1行で記述できる。UPFに対応したツールは高度なもので、コマンドを受け取り、適切なレベルでパワーゲーティングを適用することが可能だ。合成中に適用されるものもあれば、配置配線時に適用されるものもある」と説明した。

パワーゲーティング手法では、手作業またはツールの力を借りながら、アイソレーション用のフリップフロップを挿入しなければならない。「ブロックを遮断するときに、そのブロックの出力がまだ電力供給されているブロックへと渡される場合、電力が遮断されたその信号ラインが浮遊状態にならないように考慮しなければならない。その電位が閾値電圧レベルに達し、不要な電流が流れてしまう可能性がある」とKeating氏は説明する。「アイソレーションセルを配置することで出力が1か0になるようにし、不要な電流が流れないようにしておく必要がある」と同氏は指摘した。

さらに、パワーゲーティング手法ではリテンション用のフリップフロップを用いる必要がある。Keating氏は、「ブロックの電源を遮断する場合の問題の1つは、その状態を復元するための情報をどこかに保持しておかなければならないことだ」と指摘する。そのために用いられるのがリテンション用のフリップフロップである。

高速動作が要求される主要部分のフリップフロップは、閾値電圧が低いトランジスタで構成されている。つまり高速だがリーク電流が大きい。そこで、そのフリップフロップの横に、高閾値電圧で低リーク電流のリテンション用のフリップフロップのセルを配置する。このようにしておき、ブロックの電源を遮断する直前に、閾値電圧の低いフリップフロップの出力を、閾値電圧の高いリテンション用のフリップフロップに入力する。するとリテンション用のフリップフロップ以外は動作を停止し、状態がこのフリップフロップによって保持される。ブロックの電源が再び投入されたときに、リテンション用フリップフロップは閾値電圧の低いフリップフロップにデータを戻す。それにより、ブロックの状態が迅速に復元される。

Copyright © ITmedia, Inc. All Rights Reserved.