低消費電力LSIの設計技術:最新技術動向をまとめて理解!(5/5 ページ)

携帯型端末などに用いるLSIには、当然のことながら、低消費電力化の実現が要求される。しかし、昨今では、それ以外の用途に向けたASICやSoCを設計する場合でも、低消費電力設計手法の適用が必須となっている。最新のプロセス技術を用いると、必然的にリーク電流が多くなってしまうからだ。本稿では、ASIC設計者が知っておくべき、消費電力の削減手法についてまとめる。

EDAツールの現状

Frenkil氏は、「個々のEDAベンダーはさまざまな種類のツールを提供し、低消費電力設計に携わる設計者を支援しようとしている。その一方で、EDA業界全体としても、パワーインテグリティツールの提供を進めている。それにより、設計者は電力に関する設計上の決定が及ぼす影響を考慮できるようになる」と指摘する。

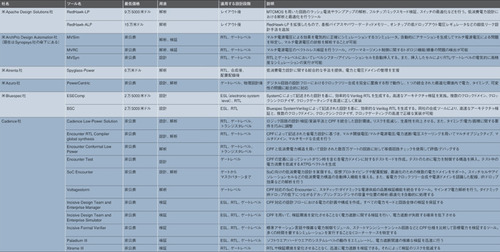

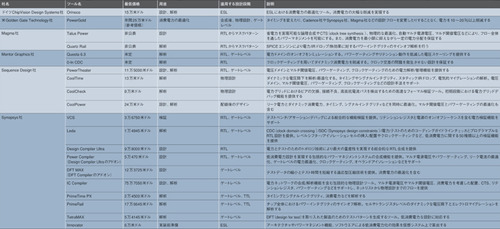

パワーインテグリティツールとは、電圧降下解析、電圧ディレーティングタイミング解析、ノイズマージン解析、パワーバスサイジングを行うツールである。多くのベンダーが、これらの問題にあらゆる角度から対処するためのツールを提供している(表1)。しかし、Keutzer氏によると、「EDA業界はいくつかの問題に対してまだ適切には対処できていない。例えば、クロックネットワークのより効率的な構成法や、透過ラッチをより効率的に使用するためのパイプライン手法など、ASIC設計者によるマイクロアーキテクチャ技法の実装を簡素化するツールを提供すべきだ」という。さらに、同氏は「電力にかかわるすべての問題を解決するEDAツールなど存在しないことは分かっている。誰もホームランは求めていない。ヒットをたくさん打ってほしいのだ」と述べた。

設計者は、さまざまな低消費電力設計手法に精通し、どのツールが自分の目標を達成するために適切であるかを調査する必要がある。

EDA業界は、設計者によるパワーマネジメントを支援する適切なツールを提供しようと努力している。最終的には、ベンダーらは設計者がタイミング、電力、シグナルインテグリティ、そして将来的には熱解析についても、それぞれの間に存在するトレードオフを検証できるような設計フローを提供したいと考えている*3)。

大手半導体企業やデザインハウス、EDA企業などは、共通の電力フォーマットを確立しようとしている。また、低消費電力化技術に対応したEDAツールは続々と登場している。しかし、EDA業界には、電力の問題を解決する前に対処しなければならない問題もまだ多く残されている。

脚注

※3…Santarini, Michael, "Thermal integrity: a must for low-power-IC digital design," EDN, Sept 15, 2005, p.37.

Copyright © ITmedia, Inc. All Rights Reserved.