DC-DCコンバータのノイズ対策[実践編]:徹底研究! 設計/実装における具体策(3/5 ページ)

本稿では、非絶縁型/スイッチング方式のDC-DCコンバータにおけるノイズ対策について、2回にわたって解説している。前回は『理論編』として、ノイズの種類やその発生メカニズムについて説明した。その内容を踏まえ、今回の『実践編』では、ノイズの発生を抑えるための基板レイアウト設計の基本、部品の選択方法、付加回路による対策手法について具体的に解説する。

部品の選択

続いて、ノイズ対策を念頭に置いた部品の選択方法について説明する。

■ローサイドMOSFET

『理論編』で説明したように、パワーMOSFETはノイズの発生源(加害者)である。従って、ローサイド(フリーホイール)MOSFETのQ2がターンオフするときと、ハイサイドMOSFETのQ1がターンオフするときのスパイク/リンギングノイズを低減させることが重要だ。

Q2がターンオフするときのノイズは、Q2のボディダイオード(ダイオード整流の場合はダイオードそのもの)のリカバリ電流IPRをエネルギー源とする。理想的には、リカバリ電流が小さく、ソフトリカバリ特性を持っているとよいのだが、一般的にはリカバリ電流が小さければ高速なハードリカバリ特性となり、選定は難しい作業となる。

最近のパワーMOSFETの中には、ボディダイオードをショットキーダイオードとして作り込んだりすることでリカバリ特性を改善したものがある。従って、まずはデータシートなどを参照して複数の製品を比較してみるとよい。最終的には、実機でリカバリ特性やスパイク/リンギング波形を観測して比較/判断することになる。

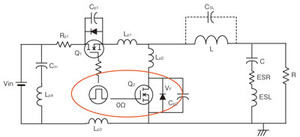

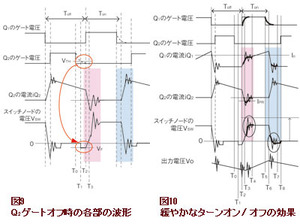

ローサイドMOSFETには、駆動回路としてのゲート抵抗は使わない(すなわち、0Ωとする)のがよい(図8)。とにかく、ローサイドMOSFETは速くオフするようにする。ローサイドMOSFETがオフするのが遅いと、ハイサイドMOSFETとローサイドMOSFETが同時にオンすることによるショートの問題(シュートスルー)が発生する危険性があるからだ。また、ゲート抵抗を0Ωとしても、パワーMOSFET内部には数Ωの抵抗が存在する。そのため、ゲートにおいて波形を観測して電圧が急速に降下していることを確認するとともに、図9に示すように、Q1がオンする直前にボディダイードによる電圧降下がきちんと行われているかどうかをオシロスコープで確認することをお勧めする。

なお、ローサイドMOSFETがオフする際のデッドタイムを調整し、ボディダイオードがオフにならないようにする方式もあるので、併せて比較してみるとよい。

■ハイサイドMOSFET

ハイサイドMOSFETのターンオン/オフが緩やかなほど、ターンオン/オフ時のスパイク/リンギングが抑制される(図10)。これは、ターンオン/オフ時にスパイク/リンギングが発生している期間に見えるQ1のオン抵抗がダンピング抵抗として作用するからである。ハイサイドMOSFETのターンオン/オフを緩やかにするには、数Ωのゲート抵抗を用いればよい。

なお、ターンオン/オフの速いMOSFETを使うと、効率は良くなるがノイズの面では悪い影響が出る。

■寄生インダクタの小さいMOSFET

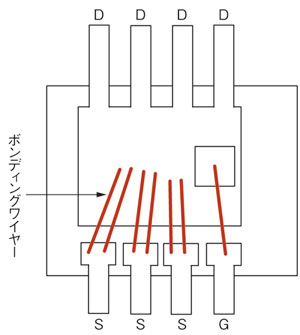

ハイサイド/ローサイドのMOSFETとしては、いずれも、寄生インダクタの小さいものを用いるべきである。MOSFETのリードおよび内部のボンディングワイヤーによる数nHの寄生インダクタンスが、ターンオフ時に生じるノイズのエネルギー源となるからだ。

比較的少ない電流しか必要ないなら、ローサイド/ハイサイドのMOSFETが1チップになっている製品などはお勧めできるものだと言える。少なくとも、MOSFET間の寄生インダクタンスは無視できるほど小さいからである。1チップでなくても、MCM(Multi-Chip Module)タイプのものであれば、通常のSOP-8パッケージなどのように外部で接続するものよりも、MOSFET間の寄生インダクタンスはかなり小さい。

図11に示すのは、SOP-8パッケージの典型的なMOSFET製品の構造である。最近は、パッケージ内のインダクタンスを低減するために、各社ともさまざまな工夫を施しているようだ。

Copyright © ITmedia, Inc. All Rights Reserved.