DC-DCコンバータのノイズ対策[実践編]:徹底研究! 設計/実装における具体策(4/5 ページ)

本稿では、非絶縁型/スイッチング方式のDC-DCコンバータにおけるノイズ対策について、2回にわたって解説している。前回は『理論編』として、ノイズの種類やその発生メカニズムについて説明した。その内容を踏まえ、今回の『実践編』では、ノイズの発生を抑えるための基板レイアウト設計の基本、部品の選択方法、付加回路による対策手法について具体的に解説する。

付加回路による対策

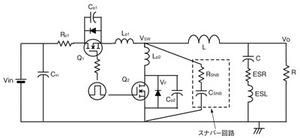

回路によるノイズの抑制法としては、スナバー回路が最も効果的だ。図12に、スナバー回路によって対策を施したDC-DCコンバータの回路図を示した。スナバー回路はサージエネルギーを発するスイッチ/ダイオードに接続すべきものである。従って、降圧型DC-DCコンバータの場合、Q1、Q2の両方に付加してもよいのだが、一般的にはQ2(もしくはフリーホイールダイオード)のドレイン‐ソース間に付加することが多い。なぜなら、Q2のリカバリ電流によるサージが大きいからである。

稿末に示した参考文献2によれば、リンギングがなくなる、すなわちいわゆるフルダンピングとなるスナバー回路の抵抗RSNBとコンデンサCSNBの値は、以下の2つの式で与えられる。

ここで、Cp2はQ2のドレイン‐ソース間容量、LpはQ1、Q2間の寄生インダクタ(図12のLp1とLp2の和)である。

この抵抗RSNBとコンデンサCSNBの値をそのまま用いると損失が大きくなるので、実際には式(1)、(2)の値を出発点としてダンピングを弱めていき、効率とノイズのトレードオフによって値を決定する。筆者の場合、過去の経験に基づき、入力電圧が12V、スイッチング周波数が500kHz程度という条件であれば、まずはCSNB=4×Cp2で試してみている。また、抵抗値RSNBの式(1)で使っている係数も、これに近い値であれば厳密に0.65である必要はない。なお、スナバー回路における損失は以下の式で与えられる。

ここで、fSWはDC-DCコンバータのスイッチング周波数である。

実験による確認

ここまでに述べた対策内容について、実機で確認してみよう。なお、パワーMOSFETとしては、スイッチング速度の速いものを選んで用いた。

表1は実験の条件を表したものである。ハイサイドMOSFETのゲート抵抗の有無、スナバー回路の有無、後述するCinラインインダクタの有無という条件を組み合わせている。

スナバー回路はローサイドMOSFETだけに付加することにした。Cp2=340pF、Lp=3nHと仮定して、式(1)、(2)と、式(3)で求まる損失とのトレードオフから、値はRSNB=3.3Ω、CSNB=1500pFとした。

Cinラインインダクタとは、入力コンデンサのESLを等価的に大きくするために、入力コンデンサに付加した擬似的なインダクタのことである。具体的には、入力コンデンサを基板から浮かし、1cm程度のリード線で接続することによって実現した。

測定は入力電圧Vinのリップル電圧(入力コンデンサの両端の電圧)、スイッチノードの電圧(Q2のドレイン‐ソース間電圧)、出力電圧Voのリップル電圧(出力コンデンサの両端の電圧)、および電波暗室でのEMI(Electromagnetic Interference)放射雑音(3m法)を対象とした(写真1)。波形の測定には、帯域が1GHzのオシロスコープを用いた。また、ノイズの影響を受けにくいよう、入力電圧Vinの端子とスイッチノードについては受動プローブとマウントジャックを使用し、出力電圧Voの端子にはFETプローブ(米Tektronix社の「P6243」)を使用した(別掲記事『ノイズの測定方法』を参照)。

それでは、測定結果を見てみよう。図13の(a)〜(d)は、表1に示した条件(a)〜(d)に対応する。(a)はオリジナルの状態であり、『理論編』の図8(本誌12月号のp.57)に示したボードをそのまま用いている。ハイサイドMOSFETにはゲート抵抗を付加しておらず、Q2にもスナバー回路を付加していない。(b)はハイサイドMOSFETのゲート抵抗のみ10Ωにした結果、(c)はローサイドMOSFETのスナバー回路のみ付加した結果である。

(a)の結果に対し、(b)、(c)では、入力部のノイズ波形、スイッチノードのノイズ波形、出力部のノイズ波形、EMI放射雑音ともに改善されていることがわかる。これらと比べると、出力部の電圧波形Voに関してはあまり変化がない。これは、出力インダクタの寄生容量が非常に小さいことと(おそらく数pF)、同インダクタ下部のレイアウトにおいて、電極パターンが十分に離れており、高周波信号パスのインピーダンスが非常に高いことからであろう。

また、入力コンデンサに等価ESLを追加した最も条件の悪い(d)を見ると、入力電圧Vinの電圧波形はターンオン/オフ時に生じるLp×di/dtによるスパイク/リンギング電圧が非常に大きくなっている。これは、入力コンデンサのESLが数nHほど大きくなっているからである。(d)のみ、測定器のレンジを2V/divとすることでスパイク/リンギングの全体が確認でき、5.98Vppもあることがわかる。同様に、スイッチノードのスパイク/リンギング波形も極めて大きい。

以上、本稿では、2回にわたり非絶縁型DC-DCコンバータにおけるノイズ対策について解説した。降圧型コンバータにおいては、入力側高周波リンギングループの寄生インダクタンスを数nHのレベルで小さく抑えることが重要である。それに対して、レイアウトや部品選定、付加回路などによってどのような対策を行えばよいかをご理解いただけたはずだ。なお、下に示す参考文献1〜4には、DC-DCコンバータのノイズに関し、理論/実践の両面で多くの有益な情報が書かれている。ぜひ参考にされたい。

参考文献

*1)『スイッチングコンバータの基礎』(著者:原田耕介、二宮保、顧文建、発行:コロナ社)

*2)K. Harada, T. Ninomiya, M. Kohno, "Optimum Design of RC snubbers for Switching Regulators", IEEE Transactions of Aerospace and Electronics Systems, Vol.AES-15, No.2, March 1979

*3)M. Nakahara, T. Ninomiya, K. Harada ;"Surge and Noise Generation in a Forward DC-to-DC Converter," IEEE Trans. on AES, Vol. AES-21, No.5, pp.619-630, Sept. 1985.

*4)『オンボード電源の設計と活用』(著者:鈴木正太郎、発行:CQ出版)

Copyright © ITmedia, Inc. All Rights Reserved.