プログラマブルなアナログICで何が変わるのか?:求められる最適な機器設計手法(2/3 ページ)

プログラマブルなアナログICに普及の兆しが見えてきている。この柔軟性の高いデバイスに対する設計者の期待は大きい。しかしながら、ブレッドボードを用いた従来の設計手法のままで、そのメリットを十分に生かすことは可能なのだろうか。柔軟性と引き換えに複雑さを増したアナログICを使う上で、適切な設計手法とはどのようなものなのか。本稿ではこの点について考察する。

メタファがもたらす影響

プログラマブルなアナログICのベンダーは、その構造をユーザーの目から隠蔽しつつ、製品の特徴を可視化するためにメタファ(比喩的表現)を使用する傾向にある。メタファにより、ユーザーにとって親しみやすいものにすると同時に、ユーザーが抱えている問題に関連深い製品だと認識してもらおうと考えているのだ。

メタファは、チップの構造はもちろん、顧客の問題に対するベンダーの観点によって異なるものとなる。例えば、初期のデジタルPLDの時代には、ベンダーはPLDの内部を、大きなNORゲートを駆動するNANDゲートの集合であると表現していた。これは、当時、慣習的に用いられていたロジック機能の表現手法に従ったものであった。FPGAが登場した当初、ベンダーは、それを数個のゲートとフリップフロップから成るロジックセルを数多く集積した大規模アレイであると表現した。いずれのメタファも、チップの実際の回路に非常に近いものだった。現在のFPGAは、当時と比較して非常に大規模なものとなっている。そのメタファにも変化が生じ、より抽象的なものとなった。今日では、FPGAはRTL(Register Transfer Level)コードを書き込むことのできる空白の板であるとし、大容量メモリーやDSPブロック、高速I/Oセルのクラスタなどが分散配置されているものと見なすのが一般的である。

プログラマブルなアナログICのメタファにも同様の傾向がある。例えばLattice社は、上述したパワーコントローラICに対して、「デジタル/アナログ入力やコンパレータ、A-Dコンバータ、D-Aコンバータ、プログラマブルロジックアレイの列」という、チップ上の実際のコンポーネント群に沿った表現を用いている。それとは対照的に、Anadigm社は、ほとんどのユーザーに対して同社のプログラマブルなアナログICを、その構成要素であるコンデンサやコンフィギュラブルアンプ、ラダー回路、プログラマブルなアナログスイッチといった観点を用いて説明することはない。むしろ、アンプ回路やフィルタなどのアナログ機能ブロックのことを強調している。Anadigm社のCOO(最高執行責任者)を務めるSimon Dickinson氏は、「より大規模なデバイスであるほど、ユーザーに対しては、チップの中身を気にすることなく、固定機能または多機能のブラックボックスとして考えるように推奨している」と述べる。

一般的に、プログラマブルなアナログICのうち、機能が限定されているものほど、そのメタファはより文字どおりの表現になる傾向にある。しかし、プログラマブルなアーキテクチャの柔軟性が高い場合には、ベンダーは2つのアプローチのうちいずれかをとることができる。つまり、Verilog-AやSPICEのネットリストなどを前提とした、アプリケーションに依存しないメタファを使用するのか、それとも単にパラメータ付きの固定機能チップとして、プログラマブルなアーキテクチャを隠蔽したメタファを使用するのかである。ベースにあるアーキテクチャではなく、メタファがユーザーによる設計手法の決定にかかわるという点において、ベンダーが提供するメタファは非常に重要だと言える。

Lattice社のマーケティングマネジャを務めるShyam Chandra氏は、同社のパワーコントローラICについて、「リセット信号やウォッチドッグなどの制御には、まだディスクリートチップが多用されている。例えば、米ON Semiconductor社の製品ラインアップには、リセット生成用だけで400もの製品がある。また、ホットスワップコントローラICは市場に約100種存在する」と述べる。こうした背景から、Lattice社は、設計者が数個の小規模な固定機能のチップを使用するイメージを表現するメタファを用いている。

設計仕様を定めるために、Lattice社製品のユーザーは、回路基板上のプロセッサやメモリー、FPGAなどのデバイスのデータシートをくまなく調査し、各チップに必要な電源投入シーケンスを決定する。それらのシーケンスをまとめ上げると、パワーコントローラの完全な状態遷移図を作成できる。「ただし、これは手作業で行わなければならない」とChandra氏は注意を促す。「おそらく3/4くらいの確率で、最初に作成した状態遷移図には誤りがある。人間は誤りを犯すものだ。しかも、データシートの仕様に不確かな部分が存在することも多い」(同氏)という。

そこでLattice社は、簡単なプログラミング言語と波形シミュレーションツールを提供している。それらによって、ユーザーがシーケンスをコーディングし、その動きを観測できるようにしたのである。シーケンスが正しければ、Lattice社製ICにその状態遷移のプログラムを書き込み、回路基板上のリセット信号や、電源をシーケンス制御するMOSFETのゲートを駆動できるように設定する。同様に、同社は定数トリミングおよびマージン検知回路の設定を支援するソフトウエアツールも提供している。既知のDC-DCコンバータ部品のライブラリを使用することにより、ツールは個々の用途におけるマージンや電圧の要件を取り込み、オンチップのコンパレータとD-Aコンバータを設定して、DC-DCコンバータ出力の監視などに必要なパラメータを設定してくれる。

続いて、電源制御以外の分野でのメタファの例を紹介しよう。米Actel社は、FPGAファミリ「Fusion」でコンフィギュラブルなAFE(アナログフロントエンド)ブロックを提供している。同社は、プログラマブルなアナログ部分について、Lattice社と同様のメタファを適用している。その一方で、Lattice社とは異なり、ユーザーがボードレベルのシミュレーションに関心があるかどうかについては懐疑的に考えている。同社のフィールドアプリケーションエンジニアであるMark Nagel氏は、以下のように述べている。

「何らかのボードシミュレーションを行う顧客は、全体の半分にも満たないと考えている。われわれはチップレベルのシミュレーションを行うために、アナログのスティミュラス波形を生成可能なツールを提供している。これをA-Dコンバータモジュールに入力することで、FPGAロジックシミュレータの『ModelSim』で使用するためのデジタル出力を生成することができる。しかし、われわれのAFEトポロジは、かなり固定的なものだ。多くの場合、ユーザーはまず事前に分解能やサンプリングレートなどの要件について検討し、AFEの設定と試行を実施する。回路基板上の部品でAFE内のアナログノードを調べたり、チップのFPGA部分に組み込まれたロジックアナライザ『Synplicity』でデジタル出力を観測したりすることができる。そのため、ユーザーは通常、ツールでAFEについてシミュレーションを実施することはなく、デジタル部のロジックのみシミュレーションで検証する」。

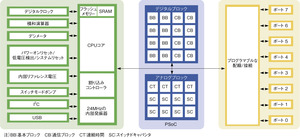

米Cypress Semiconductor社の見解は、これとは異なる。同社の「PSoC(Programmable System on Chip)」は、基本的なデジタルブロックやマイクロコントローラコアのアレイに密接に結合したアナログコンポーネントのコンフィギュラブルアレイを備えている(図2)。Cypress社のこのチップアーキテクチャは汎用向けであるため、高レベル言語を前提としたメタファと合成シミュレーションを用いた設計フローが適しているようにも思える。しかし、同社は異なる方向性を選択した。同社のフィールドアプリケーションエンジニアであるJason Baumbach氏は、「われわれのメタファは、部品カタログのようなイメージを提供する。プログラマブルなアナログアレイではない。ユーザーは何千もの構成レジスタを提供されても困惑するだけだ。そこでわれわれは、“ユーザーモジュール”のカタログを提供している」と説明する。

ここで言うユーザーモジュールとは、チップ上のアナログアレイのうち、構成済みの部分のことである。それらは、ユーザーにとっては市販のアナログコンポーネントのようなものだ。ユーザーは、このユーザーモジュールを用いてアナログ部分の回路図を作成する。その上で、通常はCypress社のPSoC開発ボードを用いて、回路図を基に直接ブレッドボードを作成する。Baumbach氏は、「ユーザーの多くは、SPICEや米The MathWorks社の『MATLAB』ですら使用していない。多くの場合、アナログ回路で実現しようとしていることは、かなり単純であることが多い」と述べる。

Copyright © ITmedia, Inc. All Rights Reserved.