プログラマブルなアナログICで何が変わるのか?:求められる最適な機器設計手法(3/3 ページ)

プログラマブルなアナログICに普及の兆しが見えてきている。この柔軟性の高いデバイスに対する設計者の期待は大きい。しかしながら、ブレッドボードを用いた従来の設計手法のままで、そのメリットを十分に生かすことは可能なのだろうか。柔軟性と引き換えに複雑さを増したアナログICを使う上で、適切な設計手法とはどのようなものなのか。本稿ではこの点について考察する。

シミュレーション手法の相違

ほとんどのICベンダーは、回路基板におけるチップ間の相互作用の様子や、アナログ部とデジタル部の相互作用の詳細を把握するためのボードレベルのシミュレーションツールを提供しようとは考えていない。従って、こうしたことについては、ユーザーの経験やデータシートから得られる情報に頼るしかない。Lattice社のChandra氏は、「電源管理の世界では、シミュレーションとは、回路図を読み、机上で深く考察することを意味する」と述べる。

しかし、Cypress社は別の方向性を目指している。「PSoCのアナログ部分は、今後さらに重要なものになる。多くの顧客が、マイクロコントローラによって動的(on the fly)にアナログアレイを再構成する方法を探究している」(同社)という。この機能は有用だが、部品カタログというメタファにはそぐわない。同社の製品マーケティングマネジャであるMark Saunders氏は、「デバイスは、ますます強力なものになっていく。それに伴って、抽象化も進めていく必要がある」と述べる。

これとは対照的に、オーストリアのaustriamicrosystems社は、比較的単純なチップのシミュレーションに対し、より広範なアプローチを試している。同社のリニア/ワイヤレス製品担当マーケティングディレクタを務めるBruce Ulrich氏は、「エンジニアは2種類に分けられる。一方は、シミュレーションに対して疑問や不信を感じるタイプの人だ。彼らは、シミュレーションを中身の薄いものだと感じている。しかし、他方では、市販のアナログICを使用しており、自身をアナログの専門家であるとは思っておらず、周波数や負荷をパラメータとする実験を支援してくれるツールがあれば便利だと感じるエンジニアも存在する」と説明する。

そこで同社は、自社のウェブサイトに米Transim Technology社の線形シミュレーションエンジン「WebSIM」へのリンクを設けた。austriamicrosystems社のパワーICのモデルや、ネットリストキャプチャツール、シミュレーションエンジン、BOM(Bill of Material)生成ツールを利用でき、ユーザーは、サイト上でパワーサブシステムのブレッドボードを設計し、パラメータや性能を調べて、部品リストを入手することが可能である。Ulrich氏は、「この仕組みではSPICEほどの精度は実現しておらず、線形近似を用いている。それでも、回路の動作の概要を把握するのには十分だ。また、スイッチングノイズや安定性の問題が生じそうな場合には警告してくれる」ことを強調する。同社は、ユーザーが同社製品ラインのほかの部品を検討できるように、モデルライブラリを拡張することを考えている。

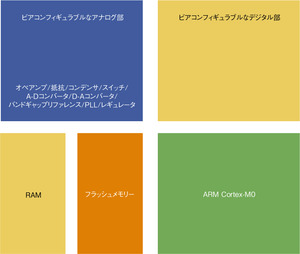

米Triad Semiconductor社は、さらに異なる状況にある。同社は、Cypress社と同様に、プログラマブルなアナログアレイとマイクロコントローラを組み合わせたチップを製造している(図3)。しかし、この場合のプログラマブルとは、フィールドプログラマブルという意味ではなく、工場でのビアプログラミングのことを指す。

Triad社のマーケティングおよびテクニカルセールス担当バイスプレジデントを務めるReid Wender氏によると、多くの場合、同社のユーザーは、シミュレーションではなく、ブレッドボードの作成から開始するという。その際には、アナログ信号パス用の市販のディスクリートなアナログ部品、デジタルロジック用のFPGA、および英ARM社のプロセッサコア「Cortex-M0」を使用することになる。「設計者の多くは市販の部品を好み、われわれのASICをそれらの仕様に合わせるよう求める」とWender氏は述べる。

顧客はブレッドボードをTriad社と共有し、同社はボードの動作を基にしてASICにおけるアナログ信号パスの伝達関数を検討/定義する。具体的には、チップレベルのシミュレーションツールを用い、顧客のブレッドボードの伝達関数に合わせてアナログアレイを構成する。Triad社は、約4週間の間にシミュレーション結果を顧客に示し、ビア用のフォトマスクデータを完成させる。顧客はTriad社のチップをブレッドボードに搭載し、検証へと進むことになる。

Wender氏によると、このフローにおいて難しいのは、アナログ信号パスとCortex-M0上で稼働するソフトウエアとを結び付けることであるという。Wender氏は、「米Keil社とともに、ミックスドシグナル周辺機能のシミュレーションについて取り組んでいる。最終的には、完全なアナログ/ミックスドシグナルシミュレータが必要になるが、これはデスクトップ型パソコンで動作する、Verilog/SPICEなどを統合した環境を低価格で構成しようとするようなものだ。これについてはまだ模索中の状況にある」と述べる。

将来的な手法

米ジョージア工科大学で進行中の研究プロジェクトからは、将来の展望がうかがえる。同大学において電気工学/コンピュータサイエンスを専門とするPaul Hasler教授は、FPAAの研究に10年間携わっている。現在のプロジェクトでは、約1000個のアナログコンポーネントと数千個のスイッチレベルコンポーネントを100個のアナログ演算ブロックに格納した大規模アレイを構築している。Hasler教授は、「完成したチップの処理能力は、おそらく市販のプログラマブルアナログアレイの10倍くらいに相当するはずだ。1TMACS(1秒間に1兆回の積和演算)に相当する信号処理を、単一のチップ、数百mWの消費電力で実行できるレベルになる」と述べる。

同氏とそのチームは、アナログ信号処理のメタファを採用し、完全な設計フローを構築した。「このICには、約10万個のプログラマブルなパラメータがある。これほどまでに複雑なものになると、手作業で処理することはできない。そこで、ブロックレベルの信号処理メタファを用いたプログラミングというアプローチを採用している」と同氏は述べる。

それでも、FPAAのように複雑なチップに対しては、ASICの設計フローのようなものが必要になる。1000個のコンポーネントから成るアナログ回路のトラブルシューティングは、ブレッドボードを用いた手法では不可能であると言ってよい。そこで、FPAAの設計フローでは、2段階のシミュレーションを採用する。

その設計フローは、まずThe Math Works社の「Simulink」からスタートする。Hasler氏のチームは、演算処理に用いるライブラリのSPICEネットリストを作成した。ユーザーは、Simulinkでシステムシミュレーションを実行し、SPICEネットリストを作成して、それをチップコンパイラに引き渡す。これにより、FPGAプログラミングファイルに相当するものが生成される。同氏は、「大抵、有効なSPICEネットリストをコンパイルすることができるが、すべてにおいて効率的なものが生成されるわけではない」と述べる。

現在、同氏のチームは、スイッチレベルのプログラミングファイルから、寄生要素を含む正確なSPICEネットリストを抽出でき、レイアウトとソースの比較が行えるツールを開発している。「バックアノテーションをSimulinkレベルまで持っていく部分がやや困難だ」とHasler氏は付け加えた。

米Cadence Design Systems社のミックスドシグナルシミュレーションマーケティング担当ディレクタを務めるJohn Pierce氏は、「将来はこのようなフローが、より単純なコンポーネントに対しても使用されるようになるかもしれない。従来の手法は、もはや固定機能のデバイスに対しても有効ではない。複数のプログラマブルデバイスをシステムに集積した場合、当然のことながら、プログラミング方法についても検討しなければならないが、そのときに何が生じるかを観測する必要もあるだろう」と述べる。さらに同氏は、「解決しなければならない問題がまだ存在する」と付け加える。

直感的には、MATLABなどのシミュレーションツールによって回路基板シミュレーションを開始すべきである。しかし、伝達関数からスイッチマトリクスを得るのは容易ではないし、回路シミュレーションレベルでも問題が生じる。「Verilog-AやSystemVerilogでは、実行時に構成レジスタの設定を変更することはできない」と同氏は述べる。しかし、構成レジスタとアナログスイッチをデバイスのネットリストの一部としてモデル化しようとすると、シミュレーションは膨大な量になってしまう。特にスイッチドキャパシタを使用している場合はそうである。

「システム環境内でプログラマブルなアナログICをシミュレーションすることは難しくない。問題は、われわれのVerilog-AMS(Analog/Mixed-signal)の世界に、プログラマブルなアナログICをいかにして取り込むかということだ」とPierce氏は述べた。

Copyright © ITmedia, Inc. All Rights Reserved.