ツールで確保するシグナルインテグリティ(2/3 ページ)

シグナルインテグリティの問題は、注意を怠ると後で災いとなって返ってくる。専用のソフトウエアツールを利用することにより、設計のなるべく早い段階で、その問題を回避するようにすることが肝要だ。本稿では、シグナルインテグリティへの対処の流れを簡単に説明した上で、各種ベンダーが提供するツールにはどのようなものがあるのかを紹介する。

プリレイアウトでの検討

シグナルインテグリティ用のソフトウエアツールは、プリレイアウトとポストレイアウトの両方をサポートする。ツールを利用することで、製品からリスクが取り除かれることも多い。

シグナルインテグリティツールは、プリレイアウトについては、チャンネルが過大なノイズを放射することなく、仕様どおりの動作を維持できるかどうかの確認に利用できる。パッケージにおける端子配列やコネクタ端子の割り当てなど、設計上の選択を支援し、プロジェクトの最後に大きな問題を抱えることのないよう支援してくれる。プリレイアウトでの解析を行う際には、チャンネルの仮想プロトタイプが正しいことと、実際のトレース長の予測が正しくなされていて、基板の寄生要素について考慮済みであることを確認する必要がある。高度なプリレイアウトツールは、チップ内で実行されるアルゴリズムについての考慮も行う。そのため、仮想チップにおけるプログラム可能なすべての設定に対して多くの実験を行い、チャンネルの能力を最大にしておく必要がある。

シグナルインテグリティツールをプリレイアウトモードで使用すれば、基板のレイアウトに関する詳細な調査が行える。レイアウトデータをシグナルインテグリティツールに入力すれば、シリアルチャンネルのパフォーマンス、チャンネルが及ぼす近隣回路への影響、その設計によって生成されるEMI放射量の概略を予測してくれる。ハイエンドのシグナルインテグリティツールであれば、信号間のクロストークや、信号に対するパワーインテグリティの影響についての検討も行える。

中核はフィールドソルバー

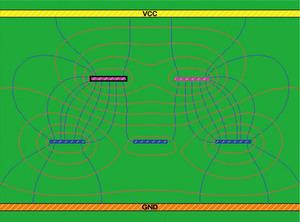

シグナルインテグリティツールは、システムの物理的構成を基に、マクスウェルの方程式を解くことで、銅線における電圧値と電流値を予測するフィールドソルバー*1)として機能する(図3)。3Dのフィールドソルバーは、複雑な設計におけるトレース、ワイヤー配線、ボードなどをモデル化することができる。3Dの方程式を解く処理は膨大なものだが、それでもシンプルな条件であれば、数分〜数時間しか要さないことが多い。しかし、通常、シリアルチャンネルは大きな基板上に存在し、数百〜数千もの信号が関連する。そのため、3Dフィールドソルバーでの解析には、数週間〜数カ月を要してしまう。

3Dフィールドソルバーを用いるシグナルインテグリティツールでは、適切な時間内で解を得るために、適宜、複雑な処理を簡略化することが行われる。そうした背景もあり、ツールに不適切な仮定を与えたり、ツールの限界を理解していなかったりすると、正しい解が得られない恐れがある。

フラットな基板の信号についてであれば、安価な2Dフィールドソルバーで解析可能である。ツールにおいては、ビアを、伝送線における容量性の不連続性としてモデル化することができる。これは、低速なチャンネルに対しては有効な方法だ。しかし、6Gbpsを超えるような条件になると、ビアが信号に及ぼす影響は非常に複雑なものとなる。このような高速チャンネルに対しては、2.5D/3Dのフィールドソルバーが必要である。Sigrity社の「Channel Designer」のような高度なツールは、ビアとコネクタに対しては3Dの手法を適用し、プレーン上のトレースに対しては2Dの手法を適用する。それにより、解析時間の短縮を図るのである。

シグナルインテグリティツールを選択する際には、演算速度と精度の間のトレードオフが基本的な検討事項となる。すべてのシミュレーションを5Gbpsレベルのチャンネルに対応させるには、損失の多い絶縁体や3次元の構造など、そのチャンネルに生じ得る微妙な問題を解決可能なツールが必要になる。また、シリアルデータを送信するチップでは、電源についても注意を払わなければならない。そのため、Channel Designerでは、温度によるチップ性能の差に加え、チャンネルにおける電源システムによる影響も考慮に入れ、現実的な条件下でのチャンネルのパフォーマンスをより適切に把握できるようにしている。

適切なツールを用いれば、周波数領域のモデルにインパルス関数を適用することができる。応答の立ち上がりエッジの前に乱れが生じる場合は、モデルに因果的な問題が存在するので、その正当性を調査する必要がある。なお、TDR(時間領域反射測定)によって抽出したモデルであれば、因果的な問題が生じることはほとんどない*2)。

脚注

※1…Rako, Paul, "Beyond Spice: Field-solver software steps in for modeling high-frequency, space-constrained circuits," EDN, Jan 18, 2007, p.41

※2…Rako, Paul, "TDR: taking the pulse of signal integrity," EDN, Sept 3, 2007, p.48

Copyright © ITmedia, Inc. All Rights Reserved.