ESD/イミュニティ試験の基礎をつかむ:デバイスレベルとシステムレベルで異なる(2/4 ページ)

電子機器の動作にさまざまな影響を与えるESD(静電気放電)への対策を講じるには、ESDの試験法について理解しておく必要がある。本稿では、デバイスレベルとシステムレベルに分けてESD試験の手法を説明する。また、産業用機器の開発で利用する機会の多いイミュニティ(耐性)試験も紹介する。

■MM試験

1990年代に登場したMM(Machine Model:マシンモデル)に基づくデバイスレベル試験は、現在はHBM試験ほど広く利用されていない。MM試験が登場した背景には、1990年代に入って製造能力を強化するために製造装置の自動化が進み一般化してきたことが挙げられる。製造装置の電源投入後に電荷の蓄積が始まり、装置内で扱うIC/電子部品にその電荷が移動して放電が起きるのだ。このようなタイプのESD現象を試験するためのモデルがMMである。MM試験の破壊モードは、HBM試験と同様であり、接合破壊、金属層溶融、ゲート酸化膜破壊などがある。

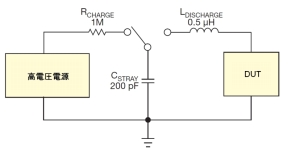

MM試験では、200pFのコンデンサと1MΩの充電用抵抗に直列に接続した高電圧電源を用いる。コンデンサを満充電の状態にしてからスイッチを使って高電圧電源と1MΩ抵抗から切り離し、0.5μHの放電用インダクタを介してDUTに接続する(図3)。高電圧電源の電圧は50〜400Vの範囲で設定することが多い。

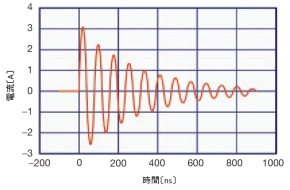

DUTに流れる電流は振動波形となっている(図4)。電流値はピークで約±3Aにもなる。この値はHBM試験のピークツーピークの約4倍である。電流持続時間もHBM試験より長く、ほぼ0Aになるまで約900nsかかる。また、MM試験時にDUTが受ける最大電力は約1.2kWになる。

MM試験では、DUTとなるIC/電子部品の各端子に対して規格にのっとった試験を実施する。DUTは、自動ESD試験機に接続された専用基板に取り付けられる。各端子の試験では、試験対象以外の端子は全てグラウンドに接続しておかなければならない。

■CDM試験

CDM(Charged Device Model:デバイス帯電モデル)に基づくデバイスレベル試験は、IC/電子部品の自動製造環境で起きやすい事象を模擬している。製造過程のIC/電子部品は、電位的に定まっていない状態(フローティング、非接地)に保持されていることが多い。この状態にある間はIC/電子部品に電荷が蓄積し続ける。そして、接地された導体にこのIC/電子部品が接触した時に放電が起こるのだ。

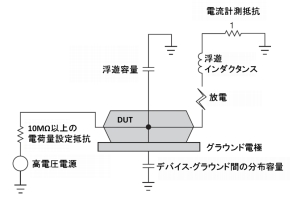

CDM試験は、自動製造環境を模擬するために、DUTは仰向けの状態(端子を上方に向けた状態)で設置して実施する。以下に、代表的なCDM試験であるリレー放電方式を例にとって説明しよう(図5)。まず、DUTと金属製電極板の間には絶縁材料を配置して、DUT、絶縁材料、電極板によって仮想的にコンデンサが形成される状態にしておく。そしてDUTの端子と高電圧電源に接続し、その電圧を所要のCDM試験条件になるまで上昇させて電荷を仮想コンデンサに蓄積する。次に、試験対象の端子にプローブを近づけて仮想コンデンサから放電現象を発生させるのだ。プローブからグラウンドに接続しているラインをモニターすることで、発生したESDの状態を確認できる。CDM試験では、正の高電圧を印加する試験と負の高電圧を印加する試験をそれぞれ3回、各端子に対して行う。つまり、各端子に対して合計6回の放電を印加することになる。

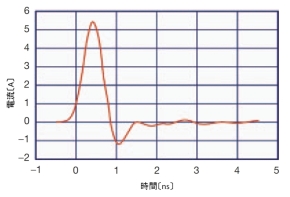

図6にCDM試験の電流波形を示す。このようにCDM試験の放電は2nsの間にほとんどが終わってしまうので、試験の実施もモデル化も簡単ではない。図6の場合、1ns以下の間に5〜6Aまで達した電流が5ns以内に消失するので、試験は簡潔だが一過性の現象を対象にすることになる。このように高速の過渡現象であることから、CDM試験の破壊モードはゲート酸化膜破壊、電荷トラップ、接合破壊が典型的である。

表1に、これら3つのESD試験の概要をまとめた。

| 試験法 | HBM試験 | MM試験 | CDM試験 |

|---|---|---|---|

| 試験電圧レベル | 2/4/8/15kV | 100/150/200V | 250/500/750/1000V |

| ピーク電流 | 1.5A | ±3A | 5〜6A |

| パルス幅 | 約150ns | 約80ns | 約1ns |

| 立ち上がり時間 | 2〜10ns | 約1ns | 400ps以下 |

| 代表的なESD破壊モード | 接合破壊、金属(イオン)侵入、金属層溶融、局部的絶縁破壊、ゲート酸化膜破壊 | 接合破壊、金属層溶融、ゲート酸化膜破壊 | ゲート酸化膜破壊、電荷トラップ、接合破壊 |

Copyright © ITmedia, Inc. All Rights Reserved.