PCI Expressの概要と高速化を支える技術:高速シリアル・インターフェイス入門(4)(1/3 ページ)

第4回となる今回は、PCI Expressを取り上げます。PCI Expressは、コンピュータ・マザーボードの拡張バスであり、それ以前のパラレルバスであるPCI(Peripheral Component Interconnect)をシリアル化したものです。

まずは、図1をご覧ください。これは、従来のPCI対応のマザーボードとPCI Express対応のマザーボードを比較したものです。左側のボードの白いコネクタがPCIで、焦げ茶のコネクタがグラフィック・カード用のAGP(Accelerated Graphics Port)です。右側のボードの白いコネクタはPCIで、黒いコネクタがPCI Expressです。

ここで注目してもらいたいのは、PCI Expressのコネクタが3つありますが、すべて長さが違うということです。中央の一番短いコネクタをx1(バイワン)と呼び、右隣のものはx4(バイフォー)、左の長いものはグラフィック・カード用のx16(バイ16)です。これはPCI Expressが持つ特徴の1つですが、必要に応じて複数のレーンを使って高速化できる機構によるものです。

PCI Expressの概要

PCI Expressは、2003年4月15日付でPCI Express Base Specification 1.0aとしてリリースされました。データ転送速度は2.5Gbpsで、8b/10bエンコードを利用しているので250MB/sの転送速度になり、その当時の32ビットのパラレル・インターフェイスPCIが132MB/sでしたので、高速化になっていません。

また、PCIの速度ではグラフィック・カードの要求する速度には対応できなかったため、AGPのx8モードにより2.13GB/sが達成されていたのですが、さらなる高速化のためにPCI Expressが開発されました。

PCI Express1本では上記のとおり250MB/sの速度ですが、これを複数使用して高速化を図っています。グラフィック・カードのように高速化が必要な場合は、16本を使うと4GB/sが達成でき、AGPの約2倍の速度が確保できます。また、必要な速度に応じて1/4/8本の構成が許されています。

このPCI Expressのシリアル通信線1本をレーンと呼び、それぞれx1、x4、x8、x16と呼びます。ピン数は、32ビット・パラレルのPCIバスが124ピンに比べて、PCI Expressのx1は36ピン、x4は64ピン、x8は98ピン、x16は164ピンとなっています。

図2は、PCI Express対応のアドイン・カード2種類を示しています。左はGen1のx1対応、右がGen2のx16対応です。転送速度は、2006年12月20日にPCI Express Base Specification 2.0がリリースされて2倍の5Gbpsになりましたが、現在2009年6月24日付でPCI Express Base Specification 3.0のドラフトがVersion 0.7になり、8Gbpsへのさらなる高速化を目指しています。このGen3では8b/10bエンコードを使わないため、約1GB/sが達成できます。

高速化を支える技術

ここからは本連載の第1回「なぜいま、高速シリアル・インターフェイスなのか」で示した高速伝送を支える技術のキーワードに従って解説をしていくことにしますが、同時に信号計測における技術的課題と対策についても説明していきたいと思います。

LVDS

第1回で高速化に有効な手法として低振幅を上げましたが、PCI Expressでは、差動信号の振幅で最低0.8V、最高1.2Vと規定されています。立ち上がり時間(20〜80%)は、Gen1の2.5Gbpsでは最短で50ps、Gen2の5Gbpsでは最短で30psと規定されています。ここでもやはり差動伝送が用いられます。

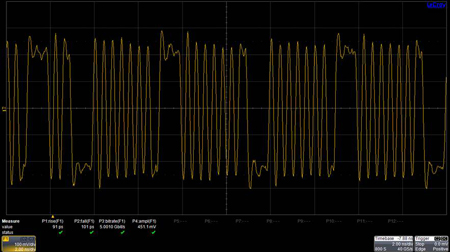

図3には、PCI Express Gen2の信号を示しています。立ち上がり時間が100psを切っていますが、オーバーシュートが非常に大きく見えます。これは、デエンファシスと呼ばれる処理がされているからですが、このことは後で説明することにします。

CRU(Clock Recovery Unit)

PCI Expressでは、前回紹介したSATAと同様にクロックはデータ信号に埋め込まれているエンベッデド・クロック方式を使っています。PCI Expressは、前述のとおり複数のレーンを使って高速化を実現しており、パラレル通信と変わらないのではないかと思われるかもしれませんが、パラレル通信の場合のように共通のクロックがあるわけではなく、個々のレーンにおいてそれぞれCRUを使ってクロックを再生します。

PCI Expressの場合には、CRUの特性が規格として規定されるようになったのは2005年3月28日付のRevision 1.1からです。規格ではTransmitter PLL BW Limitsとして送信器側のPLLと、Eye Measurement Clock Recovery Functionとして受信機側のPLLが規定されていますが、受信機のPLLはSATAと同様、送信器信号評価用に規定されたものです。帯域が1.5MHzとの1次特性であると規定されています。

ジッタ計測のより詳しい手法については、規格ではなくホワイトペーパーという形で出されており、Revision 1.1 に先駆けて2005年2月11日付のPCI Express Jitter and BER Revision 1.0で示されています。Gen 2の5GS/sの速度ではより厳格なジッタが規定されており、特に送信機側のPLLの規定が厳格化されています。

Copyright © ITmedia, Inc. All Rights Reserved.