PCI Expressの概要と高速化を支える技術:高速シリアル・インターフェイス入門(4)(2/3 ページ)

第4回となる今回は、PCI Expressを取り上げます。PCI Expressは、コンピュータ・マザーボードの拡張バスであり、それ以前のパラレルバスであるPCI(Peripheral Component Interconnect)をシリアル化したものです。

伝送線路とISI

PCI Expressでは、SATAと同様にホストからデバイス、デバイスからホストの個々の方向に専用の差動信号ペアが割り当てられている全二重通信になっています。伝送路による信号の減衰はGen1で最大13.2dB見込まれています。

さて、伝送路における減衰の要因としては、導通損失があります。線路の抵抗によって減衰するものですが、信号が高速になると、導体の表面に偏って流れるようになる(表皮効果)ため高い周波数の信号ほど減衰量が大きくなります。

もう1つの要因として絶縁体の誘電損失があります。この誘電損失も周波数が高くなるにつれて大きくなります。特にプリント基板に用いられるガラス基板(FR4)の誘電損失は大きくなりますので、一般的なマザーボードのパターン設計を考えると、損失をあらかじめ考慮するように考えられています。周波数が高くなるにつれて減衰が大きくなると信号はどのような影響を受けるでしょうか。

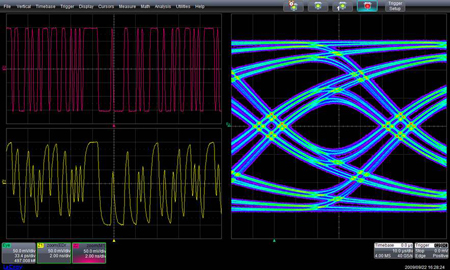

図4にはPCI Express Gen2と同等の5Gbpsの信号で起きるISIを示しています。図の左上に示されているのは、送信器から送られる理想的な信号波形を示していますが、その下の波形は丸くなっており、短い幅の信号振幅が小さくなっているのが分かります。これが伝送線によって減衰した波形です。

先ほど説明したように表皮効果や誘電損失により高周波の信号ほど損失が大きくなるため、ローパスフィルターを通したような波形になっています。この信号を基に描いたアイパターンが右に示されていますが、アイパターンの線が複数に分かれているのが分かります。クロスポイントは16個あるように見えます。

こうした現象をISI(Inter-Symbol Interference:符号間干渉)と呼びます。周波数に依存する減衰が発生すると、ISIが起こりますが、PCI ExpressではこのISIが起きることは織り込み済みです。

デエンファシス

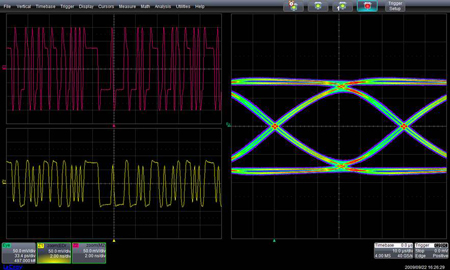

前述のとおり、PCI Expressでは、ISIが伝送線によって起きることは織り込み済みなのですが、このISIを補正する手法としてデエンファシスという手法が採用されています。図4の波形を見ると、短い幅の信号の振幅が小さくなっているだけでなく、幅の広い信号でも肩の部分が落ちているのが分かります。こういうように受信側で振幅が落ちる部分とその量があらかじめ分かっていれば、信号を送る際に事前に強調しておくことで補正できます。

この手法をプリエンファシスと呼びます。プリがあらかじめ、エンファシスが強調するという意味でこの名前があります。しかし、これは信号の高周波成分を増幅することなのでEMCでは不利になります。そこで、デエンファシスでは、受信側で振幅が落ちる部分は操作せず、振幅が落ちない部分を、逆にあらかじめ振幅を落として送信する操作をします。

受信側でISIの効果を補正するという意味ではプリエンファシスもデエンファシスも同じです。図5にはデエンファシスの効果を示しました。左上の信号がデエンファシスを掛けた信号、その下には受信側の信号、振幅差が改善されていることが分かります。左のアイパターンもきれいになっています。

PCI ExpressのGen1ではデエンファシスは3.5dBと規定されていますが、Gen2では5Gbpsと高速化しているので、3.5dB以外に6dBという規定が追加され、さらに大きな減衰にも対応できるようになっています。

アイパターン

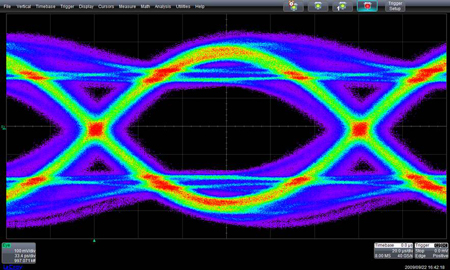

デエンファシスを掛けると、伝送線でISIが起きても受信側の信号のゆがみを改善することができますが、一方送信器側では、逆にISIが発生するために通常のアイパターンでは図6のような絵になってしまい正しく評価することができません。

正しく評価をするためには、2つの振幅の規格に対応する信号を分離して評価しなければなりません。デエンファシスを掛けると立ち上がりエッジまたは立ち下がりエッジ直後の1ビットの振幅は大きく、それ以外のビットの振幅は減衰されています。

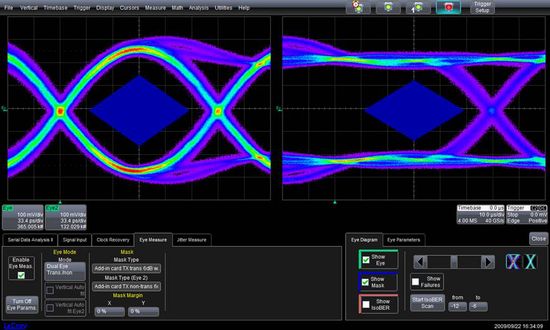

エッジ直近のビットをトランジション・ビット、それ以外の減衰されたビットをデエンファシス・ビットと呼び、アイパターンを描く際にソフトウェアで区別して2つのアイパターンを描きます。図7には左側にトランジション・ビット、右側にデエンファシス・ビットのアイパターンが描かれています。よく見ると描かれたマスクの大きさが違うことが分かります。規格では送信側のマスクがトランジション・ビットとデエンファシス・ビットで別々に規定されています。

Gen2ではデエンファシスが3.5dBと6dBの2種類が規定されているのと、クロストークを勘案してより多くのマスクが規定されています。ここでは、6dBのデエンファシスを掛け、クロストークがない場合のトランジション・ビットとデエンファシス・ビットのマスクをおのおののアイパターンに適用しています。

Copyright © ITmedia, Inc. All Rights Reserved.