ƒrƒbƒgŒë‚è—¦ƒeƒXƒ^پ[‚ًٹب’P‚ةچى‚éپFDesign Ideas Œv‘ھ‚ئƒeƒXƒg

ƒfƒWƒ^ƒ‹’تگM‚ة‚¨‚¢‚ؤٹî–{‚ئ‚ب‚é‘ھ’èٹيپAƒrƒbƒgŒë‚è—¦ƒeƒXƒ^پ[‚ًپAˆہ‰؟‚ةگ»چى‚·‚éƒAƒCƒfƒA‚ًڈذ‰î‚·‚éپB

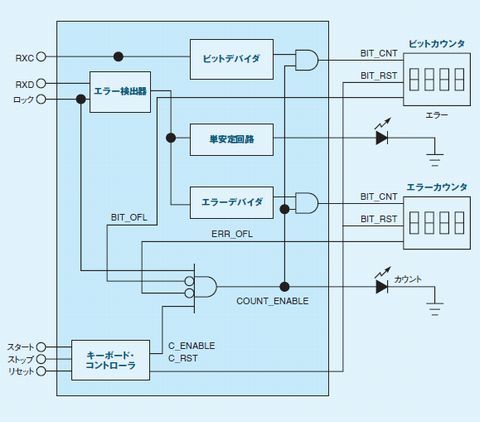

پ@ƒrƒbƒgŒë‚è—¦پibit error rateپFBERپjƒeƒXƒ^پ[‚حƒfƒWƒ^ƒ‹’تگM‚ة‚¨‚¢‚ؤٹî–{‚ئ‚ب‚é‘ھ’èٹي‚إ‚ ‚éپB‘½‚‚جژs”جBERƒeƒXƒ^پ[‚ھ“üژè‰آ”\‚إ‚ ‚é‚ھپA‚»‚ê‚ç‚ج‘م‚ي‚è‚ةˆہ‰؟‚ب‚à‚ج‚ًگفŒv/گ»چى‚·‚邱‚ئ‚à—eˆص‚¾پBگ}1‚ةژ¦‚·‰ٌکH‚حژs”ج‚جBERƒeƒXƒ^پ[•ہ‚جگ«”\‚ً—L‚·‚é‚ھپA•\ژ¦‚³‚ꂽƒfپ[ƒ^‚ةٹî‚أ‚¢‚ؤژèŒvژZ‚إŒ‹‰ت‚ًڈo‚·•K—v‚ھ‚ ‚éپB‚±‚جƒeƒXƒ^پ[‚حژَگMƒrƒbƒgگ”‚ئژَگM‚µ‚½ƒGƒ‰پ[ƒrƒbƒgگ”‚µ‚©•\ژ¦‚µ‚ب‚¢‚½‚كپABER‚ً‹پ‚ك‚é‚ة‚ح“d‘ى‚ب‚ا‚ً—p‚¢‚ؤپA•\ژ¦‚³‚ꂽƒfپ[ƒ^‚©‚çژZڈo‚µ‚ب‚¯‚ê‚خ‚ب‚ç‚ب‚¢پB

پ@گ}1‚جƒeƒXƒ^پ[‚حپAFPGA‚âCPLD‚ج‚و‚¤‚بپAƒvƒچƒOƒ‰ƒ}ƒuƒ‹پEƒچƒWƒbƒNIC‚ً1Œآ‚ئپA2Œآ‚جƒJƒEƒ“ƒ^پEƒ‚ƒWƒ…پ[ƒ‹‚ً—p‚¢‚ؤچى‚邱‚ئ‚ھ‚إ‚«‚éپBƒJƒEƒ“ƒ^پEƒ‚ƒWƒ…پ[ƒ‹‚حپA‰tڈ»‚ـ‚½‚حLED‚ًژg—p‚µ‚½‚à‚ج‚إپA4Œ…ˆبڈم‚ً•\ژ¦‚إ‚«پAƒIپ[ƒoپ[ƒtƒچپ[•\ژ¦‹@”\‚ھ•t‚¢‚ؤ‚¢‚éژs”ج•i‚ً—p‚¢‚éپB‚ـ‚½پAƒfپ[ƒ^ƒNƒچƒbƒNژüٹْ‚ج”¼•ھ‚ظ‚ا‚ج‹·‚¢ƒpƒ‹ƒX•‚جگMچ†‚ة‚à‘خ‰‚إ‚«‚ب‚¯‚ê‚خ‚ب‚ç‚ب‚¢پB

گ}1پ@ٹبˆصBERƒeƒXƒ^پ[‚ج‰ٌکHگ}

‰½‚ھ‚µ‚©‚جƒvƒچƒOƒ‰ƒ}ƒuƒ‹پEƒچƒWƒbƒN‚ئ2Œآ‚جƒJƒEƒ“ƒ^پEƒ‚ƒWƒ…پ[ƒ‹‚ة‚و‚ء‚ؤپAٹب’P‚بƒrƒbƒgŒë‚è—¦ƒeƒXƒ^پ[‚ًگفŒvپEگ»چى‚إ‚«‚éپB

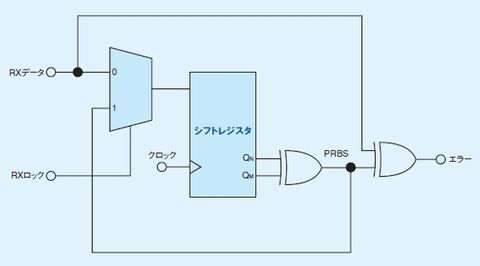

پ@گ}2‚ةƒGƒ‰پ[Œںڈoٹي‚جژه—v•”•ھ‚ًژ¦‚·پB‚±‚جŒںڈoٹي‚حپA‘—گM‹@‚ئ“¯‚¶‹[ژ——گگ”ƒrƒbƒgپEƒVپ[ƒPƒ“ƒXپiPRBSپj”گ¶ٹي‚ً—p‚¢‚ؤ‚¢‚é‚ھپA1‚آ‚جژdٹ|‚¯‚ھ‰ء‚¦‚ç‚ê‚ؤ‚¢‚éپB‘ھ’è’†‚ج•œ’²ٹي‚ھƒچƒbƒN‚³‚ê‚ؤ‚¢‚ب‚¢‚ئ‚«‚ة‚حپAƒVƒtƒgƒŒƒWƒXƒ^‚حژَگMƒfپ[ƒ^‚ًƒچپ[ƒh‚µپAƒGƒ‰پ[ƒrƒbƒg‚جŒvگ”‚حچs‚ي‚ب‚¢پBٹe•œ’²ٹي‚ح“ء•ت‚بƒoپ[ƒXƒgپEƒ‚پ[ƒh•œ’²ٹي‚ًڈœ‚«پA‚ا‚ج•œ’²ٹي‚إ‚àBER‚حƒVƒXƒeƒ€‚ھپuƒچƒbƒN‚³‚ꂽپv‚±‚ئ‚ً–¾ژ¦‚·‚é‘O‚ة‚ ‚éŒِڈجƒŒپ[ƒg‚ـ‚إŒ¸ڈ‚·‚éپB‚±‚ج‚و‚¤‚ة‚µ‚ؤپAƒVƒtƒgƒŒƒWƒXƒ^‚حچ‚‚¢ٹm—¦‚إ“ü—حƒVپ[ƒPƒ“ƒX‚ةژ©Œب“¯ٹْ‚³‚ê‚éپB

گ}2پ@ƒGƒ‰پ[Œںڈo‰ٌکH

ƒGƒ‰پ[Œںڈo‰ٌکH‚حپAƒVƒtƒgƒŒƒWƒXƒ^‚ةژَگMƒfپ[ƒ^‚ًƒچپ[ƒh‚·‚é‚©پA‚ ‚é‚¢‚حƒچپ[ƒJƒ‹‚ةگ¶گ¬‚µ‚½‹[ژ——گگ”ƒrƒbƒgپEƒVپ[ƒPƒ“ƒXپiPRBSپj‚ًƒچپ[ƒh‚·‚é‚©‚ًپAƒچƒbƒNگMچ†‚ة‚و‚ء‚ؤگ§Œن‚·‚éپB

پ@•œ’²ٹي‚ھƒچƒbƒN‚³‚ê‚é‚ئپAƒچƒbƒNگMچ†‚ھƒ}ƒ‹ƒ`ƒvƒŒƒNƒT‚جڈo—ح‚ًگط‚è‘ض‚¦‚ؤƒچپ[ƒJƒ‹‚ةƒfپ[ƒ^‚ً”گ¶‚·‚éپB‚±‚جƒfپ[ƒ^‚حپA“`‘—‚³‚ê‚ؤ‚«‚½ƒfپ[ƒ^‚ج‚ح‚¸‚إ‚ ‚éپBƒچپ[ƒJƒ‹”گ¶ƒfپ[ƒ^‚ھƒVƒtƒgƒŒƒWƒXƒ^‚ة“ü—ح‚³‚êپA“¯ژ‚ة‘ھ’è‚ھچs‚ي‚ê‚éپBژَگMƒfپ[ƒ^‚ئƒچپ[ƒJƒ‹”گ¶ƒfپ[ƒ^‚جٹش‚ة‘ٹˆل‚ھ‚ ‚ê‚خپA‚»‚ê‚ھƒrƒbƒgƒGƒ‰پ[‚ئ‚ب‚éپBƒJƒEƒ“ƒ^‚ھƒpƒ‹ƒX‚ًƒJƒEƒ“ƒg‚µ‚ؤ‚¢‚éŒہ‚èپAƒGƒ‰پ[گMچ†‚حRZƒtƒHپ[ƒ}ƒbƒg‚جƒNƒچƒbƒN‚ئˆê‘ج‚ة‚ب‚ء‚½‚à‚ج‚إ‚ب‚¯‚ê‚خ‚ب‚ç‚ب‚¢پB‚±‚ج‚و‚¤‚ة‚·‚é‚ئƒeƒXƒ^پ[‚ھ2‚آ‚جکA‘±‚µ‚½ƒGƒ‰پ[‚ً1‚آ‚جƒGƒ‰پ[‚ئƒJƒEƒ“ƒg‚µ‚ب‚¢پB

پ@•œ’²ٹي‚ھƒچƒbƒN‚³‚ê‚é’¼‘O‚ةƒGƒ‰پ[‚ھ”گ¶‚·‚é‚ئپAƒVƒtƒgƒŒƒWƒXƒ^‚جڈ‰ٹْگف’è‚ھ‹¶‚ء‚ؤ‚µ‚ـ‚¢پAƒچپ[ƒJƒ‹پEƒVپ[ƒPƒ“ƒX‚ئژَگMƒVپ[ƒPƒ“ƒX‚ج‘ٹٹض‚ھ‘ه•‚ة‚¸‚ê‚éپB‚»‚جŒ‹‰تپA‚±‚جڈêچ‡‚جBER‚ح0.5‹ك‚‚ة‚ب‚éپB‚±‚جŒë‚ء‚½ڈَ‘ش‚ح—eˆص‚ةŒںڈo‚إ‚«پA‘ھ’è‚ًچؤƒXƒ^پ[ƒg‚·‚邱‚ئ‚ھ‚إ‚«‚éپB

پ@گ}1‚ةژ¦‚·ƒAپ[ƒLƒeƒNƒ`ƒƒ‚إ‚حپAƒGƒ‰پ[ƒrƒbƒgگ”‚ئƒrƒbƒgگ”‚ًپAƒGƒ‰پ[ƒfƒoƒCƒ_‚¨‚و‚رƒrƒbƒgƒfƒoƒCƒ_پEƒuƒچƒbƒN‚إ•ھٹ„‚·‚邱‚ئ‚ھ‚إ‚«‚éپBƒGƒ‰پ[گ”‚ح1پA10پA100پA1000‚إٹ„‚邱‚ئ‚ھ‚إ‚«پAƒrƒbƒgگ”‚ح104پA105پA106پA‚¨‚و‚ر107‚إٹ„‚邱‚ئ‚ھ‚إ‚«‚éپB‚±‚ج•ھٹ„‹@”\‚ة‚و‚èƒeƒXƒ^پ[‚حپAƒeƒXƒ^پ[‚ھƒGƒ‰پ[ƒJƒEƒ“ƒgگ”‚ً•ھٹ„‚µ‚ؤ’ل‚¢’l‚ة‚µ‚ب‚¯‚ê‚خ‚ب‚ç‚ب‚¢‚و‚¤‚ب’ل•iژ؟‚جگMچ†‚ً‘ھ’è‚إ‚«پA‚³‚ç‚ةƒrƒbƒgگ”‚ج•ھٹ„‚ ‚é‚¢‚ح’·‚¢‘ھ’èژüٹْ‚ھ•K—v‚ئ‚ب‚é‚و‚¤‚بڈَ‹µ‚ة‚ي‚½‚éBER”حˆح‚à‘ھ’è‰آ”\‚ئ‚ب‚éپB

پ@ٹeƒuƒچƒbƒN‚حپA2Œآ‚جƒXƒCƒbƒ`‚ة‚و‚ء‚ؤپAٹب’P‚ة•ھٹ„گ”‚ًŒˆ‚ك‚邱‚ئ‚ھ‚إ‚«‚éپBٹشˆل‚¢‚ً”ً‚¯‚邽‚ك‚ةپA•ھٹ„گ§Œن‚إ‚حپAƒfƒBƒXƒvƒŒƒCڈم‚جڈ¬گ”“_‚àگ§Œن‚·‚é‚و‚¤‚ة‚µ‚½‚ظ‚¤‚ھ‚و‚¢پB‚ـ‚½پAƒfƒBƒXƒvƒŒƒC‚ج‰؛•”‚ةژwژ¦ƒ‰ƒxƒ‹‚ً•t‚¯‚ؤپAژہچغ‚جچ\گ¬‚ج‚½‚ك‚ج‘”{—¦‚ًژ¦‚·‚و‚¤‚ة‚·‚é‚ئ‚و‚¢پB

پ@‚à‚¤1‚آ‚ج“ء’¥‚حƒIپ[ƒoپ[ƒtƒچپ[‚ةٹض‚·‚é‚à‚ج‚إ‚ ‚éپB‚¢‚¸‚ê‚©‚جƒJƒEƒ“ƒ^پEƒuƒچƒbƒN‚ھƒIپ[ƒoپ[ƒtƒچپ[‚·‚é‚ئپAگ}1‚ج‰ٌکH‚حپABIT_OFL‚¨‚و‚رERR_OFLƒtƒ‰ƒbƒO‚ة‚و‚èپA‚½‚¾‚؟‚ةƒGƒ‰پ[ƒJƒEƒ“ƒg‚ً’âژ~‚·‚éپB‚±‚ج‹@”\‚ح–³گl‘ھ’è‚âپA’·‚¢ژüٹْ‚ج‘ھ’è‚ًچs‚ء‚ؤ‚¢‚é‚ئ‚«‚ةپAƒeƒXƒ^پ[‚ھٹشˆل‚ء‚½ƒfپ[ƒ^‚ً•\ژ¦‚µ‚ب‚¢‚و‚¤‚ة‚·‚邽‚ك‚ج‚à‚ج‚إ‚ ‚éپBBIT_OFL‚¨‚و‚رERR_OFLƒtƒ‰ƒbƒO‚ھƒAƒNƒeƒBƒu‚ة‚ب‚é‚ئپACOUNT_ENABLEگMچ†‚ًƒ^پ[ƒ“ƒIƒt‚·‚éپB

پ@ƒXƒ^پ[ƒgپAƒXƒgƒbƒvپA‚¨‚و‚رƒٹƒZƒbƒgƒLپ[‚ح‚±‚ج‘•’u‚ًگ§Œن‚·‚邽‚ك‚ج‚à‚ج‚إ‚ ‚éپB‚±‚ê‚ç‚ح—LŒہƒXƒeپ[ƒgƒ}ƒVƒ“‚ً‹ى“®‚µپA‚»‚ê‚ة‚و‚ء‚ؤپA•دگ”C_ENABLE‚¨‚و‚رC_RESET‚ًگ¶گ¬‚·‚éپBC_ENABLE‚حƒrƒbƒg‚¨‚و‚رƒGƒ‰پ[‚جƒJƒEƒ“ƒg‚ًگ§Œن‚µپAC_RESET‚حƒJƒEƒ“ƒ^‚جƒٹƒZƒbƒg‚ًگ§Œن‚·‚éپB

Design Ideasپ`‰ٌکHگفŒvƒAƒCƒfƒAڈW

پyƒAƒiƒچƒO‹@”\‰ٌکHپzپFƒtƒBƒ‹ƒ^‰ٌکH‚â”گU‰ٌکHپAƒZƒ“ƒTپ[‰ٌکH‚ب‚ا

پyƒpƒڈپ[ٹضکA‚ئ“dŒ¹پzپFƒmƒCƒY‚ج’لŒ¸ژè–@پA•غŒى‰ٌکH‚ب‚ا

پyƒfƒBƒXƒvƒŒƒC‚ئƒhƒ‰ƒCƒoپzپFLED‚جگ§ŒنپAٹˆ—p–@‚ب‚ا

پyŒv‘ھ‚ئƒeƒXƒgپzپFٹبˆصƒeƒXƒ^پ[‚جگفŒv—لپA‹Œژ®‚جŒv‘ھ‘•’u‚ج—LŒّ‚بٹˆ—p–@‚ب‚ا

پyگMچ†Œ¹‚ئƒpƒ‹ƒXڈˆ—پzپF‚»‚ج‘¼‚جƒ†ƒjپ[ƒN‚ب‰ٌکH

پ¦–{‹Lژ–‚حپA2008”N7Œژ29“ْ‚ةEDN Japan—صژ‘ٹ§‚ئ‚µ‚ؤ”ٹ§‚µ‚½پuژى‹ت‚ج“d‹C‰ٌکH200‘Iپv‚ةŒfچع‚³‚ꂽ‚à‚ج‚إ‚·پB’کژز‚جڈٹ‘®‚âژذ–¼پA•”•i‚ج•i”ش‚ب‚ا‚حŒfچع“–ژ‚جڈî•ٌ‚إ‚·‚ج‚إپA‚ ‚ç‚©‚¶‚ك‚²—¹ڈ³‚‚¾‚³‚¢پB

پuژى‹ت‚ج“d‹C‰ٌکH200‘IپvپFEDN Japan‚ج‰ٌکHƒAƒCƒfƒAٹٌچeƒRƒ‰ƒ€پuDesign Ideasپv‚ً1چû‚ة‚ـ‚ئ‚ك‚½‚à‚جپB2001پ`2008”N‚ةŒfچع‚³‚ꂽ‹Lژ–‚ج’†‚©‚ç200–{‚ًŒµ‘I‚µپA5‚آ‚جƒJƒeƒSƒٹ‚ة•ھ‚¯‚ؤژûک^‚µ‚½پB

ٹضکAƒLپ[ƒڈپ[ƒh

‰ٌکH | ƒ}ƒCƒRƒ“ | ƒfƒBƒXƒvƒŒƒC | Design Ideas | ‰tڈ» | ƒtƒٹپ[ƒXƒPپ[ƒ‹پEƒZƒ~ƒRƒ“ƒ_ƒNƒ^

Copyright © ITmedia, Inc. All Rights Reserved.