小型で低コストと低消費電力を達成、量産用途向けミッドレンジFPGA:ラティスセミコンダクター ECP5ファミリ(1/2 ページ)

ラティスセミコンダクター(以下、ラティス)の「ECP5」ファミリは、通信システムなどに搭載されるASICやASSPの機能を補完するコンパニオンチップとして仕様を最適化したFPGAである。競合メーカーの同等機能品に比べて、価格は最大40%安く、消費電力は最大30%の削減を可能とした。

ラティスセミコンダクター(以下、ラティス)は2014年4月10日(米国時間)、通信システムなどに搭載されるASICやASSPの機能を補完するためのコンパニオンチップ向けに仕様を最適化したFPGA「ECP5」ファミリを発表した。競合メーカーの同等機能品に比べて、価格は最大40%安く、消費電力は最大30%の削減を可能とした。スモールセル基地局の他、マイクロサーバや監視カメラ、4Kテレビなどの用途に向ける。

一般的なハイエンドFPGAは、28nmやそれ以降の最先端プロセス技術を用いて、高速/高性能なシステムレベルの機能をワンチップに集積できる製品を目指している。このため、消費電力の増加やチップコストの増大につながっていた。これに対して、ミッドレンジFPGAの領域にあるECP5ファミリは、筐体が小さく放熱設計にも制約があり、その上システムのコスト削減が求められている量産製品などの用途を主なターゲットに開発した。特に、通信やネットワーク、画像処理などを行うASICやASSPを用いたシステム設計において、ASICなどの機能を補うための回路を、迅速かつ低コストで追加できることも、ECP5ファミリを活用する大きなメリットである。

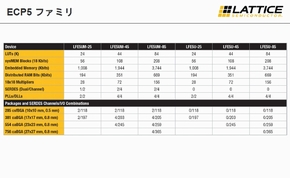

ECP5ファミリは、ASICやASSPのコンパニオンチップとして利用するのに適したアーキテクチャを採用している。例えば、ロジックセル内のルックアップテーブル(Look Up Table:LUT)数は、2万5000〜8万5000に抑えている。このため、配線リソースなどを最適化することができ、競合の同等性能品に比べて、価格を40%削減することが可能となった。ICチップの価格は現時点で公表されていないが、「価格のイメージは、ほぼ1米ドルあたり5000 LUT」(ラティスセミコンダクターのエリア・テクニカル・マネージャを務める菅原昭治氏)と話す。さらに、シリコンの面積を節約できるデュアルチャネルSERDESの採用や、用途を考慮してDSP性能の最適化を図ったこともコスト削減につながったという。

Copyright © ITmedia, Inc. All Rights Reserved.