CAEのV&V失敗事例(その1):SPICEの仕組みとその活用設計(番外編)

本連載の主目的である“分かって設計する”という観点から、CAEのV&Vのミスから新聞などに掲載されてしまった事例を“番外編”としてご紹介します。紹介する事例は、北海でオイルとガスを産出する海上プラットフォーム(Sleipner A platform)の基礎部が破損して1991年8月23日、ノルウェーStavanger沖のGandsfjordenにて沈没した事例です。

Spiceでは失敗してもニュースになることはなく、公開される失敗事例はどうしても影響の大きいFEMツールを用いた構造解析関係の記事が中心になります。今回紹介する事例は、北海でオイルとガスを産出する海上プラットフォーム(Sleipner A platform)の基礎部が破損して1991年8月23日、ノルウェーStavanger沖のGandsfjordenにて沈没した事例です。

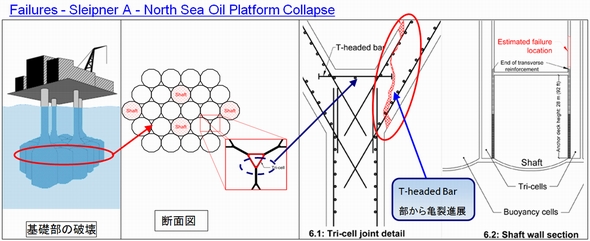

Failures-Sleipner A-North Sea Oil Platform Collapse (http://failures.wikispaces.com/Sleipner+A+-+North+Sea+Oil+Platform+Collapseより引用)

同じ内容が、http://www.ftr.co.jp/n/common/pdf/event_ftr_seminar_yokohama_2013_kouen.pdf[PDFデータ]でも紹介されています。こちらはV&Vとしての資料です。

詳しくは該当ページを参照していただくとして、要点は多角形のパイプ状の柱を接続しているT-headed Barと呼ばれる三角形状の構造の応力解析時の人的ミスです。先のページにも

『the finite element mesh used to analyze the tri-cells was too coarse to predict the shear stress accurately.The flawed analysis and post-processing of the tri-cell design led to shear forces being underestimated by some 45%』

『三角セルの解析に使われる有限要素のメッシュはせん断応力を予測するには粗すぎた。三角セル設計の損傷解析と後処理はせん断力を45%程過少評価に導いた』(筆者訳)

と記載があるように、技術者ではなく応力解析ツールのオペレータが出した結果を採用したようです。あるいは本解析前の予備解析の結果が一人歩きしたのかも知れません。

つまり、FEMによる応力解析であればメッシュサイズ〜応力の関係は必ず把握しておくべきものですが、その検討を怠り、さらにはレポートをチェックする立場の人も見逃したようです。

この応力のメッシュ依存性チェックの重要性は栗崎彰さんの「設計者CAEを始める前にシッカリ学ぶ有限要素法(6)」やCAE懇話会の「解析塾 基礎編」講座でも力説されている基本的なポイントです。

このミスをSpiceでの回路解析に置き換えれば、粗い時間間隔の過渡解析でスパイク電圧の評価を行い、耐圧オーバーで半導体が破壊したことに相当します。また、実測においても周波数特性やサンプリング速度の不足しているデジタルオシロで測定すれば同様の見逃しは生じます。

この点については既に本シリーズの連載4回目、5回目の過渡解析でその時間依存性のメカニズムを説明するとともに、

連載9回目の「解析の注意すべき事項」

として再び説明しています。当然、Spiceでは時間刻みを変えてみてスパイク電圧の変化を調べる、実測であればデジタルオシロスコープの周波数特性や、波形の中にサンプリング点が充分にあるか?などは設計者が確認しなければならないのです。

ツールがFEMからSpiceに変わっても注意するポイントに大差はないということです。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

SPICE応用設計(その7):W.C解析と設計品質

SPICE応用設計(その7):W.C解析と設計品質

今回は、Spiceを少し離れて他のCAEツールのワーストケース解析について簡単に説明するとともに、今までの連載で触れてこなかった解析機能の中から有益と思われる一部の機能について説明をしていきます。 SPICEの過渡解析(その1):キャパシタンス素子の場合

SPICEの過渡解析(その1):キャパシタンス素子の場合

過渡解析とは、いわゆる時間的に変化する特性についての解析である。SPICEを用いた回路解析では、時間的に電圧や電流が変化する部品としては、キャパシタンス素子とインダクタンス素子がある。第4回では、キャパシタンス素子使う場合の過渡解析を取り上げる。 SPICEの過渡解析(その2):インダクタンス素子の場合

SPICEの過渡解析(その2):インダクタンス素子の場合

SPICEの過渡解析では、第4回で紹介したキャパシタンス素子の他に、インダクタンス素子も対象となる。第5回では、このインダクタンス素子を用いた回路の過渡解析について取り上げる。また、理想電圧源の組み込みについても説明する。 解析実行エラーの原因と対策(その4)

解析実行エラーの原因と対策(その4)

第9回では、正帰還回路と初期条件の重要性、および解析エラーを回避する解析手法の選択について説明する。併せて、4回にわたって説明してきた解析実行エラーの原因と対策についても簡単にまとめておこう。