400–œƒچƒWƒbƒNƒZƒ‹‚ًڈWگدپA20nm FPGA‚جڈo‰×‚ًٹJژnپFƒUƒCƒٹƒ“ƒNƒX Virtex UltraScale VU440

ƒUƒCƒٹƒ“ƒNƒX‚حپA20nmƒvƒچƒZƒX‹Zڈp‚ً—p‚¢400–œƒچƒWƒbƒNƒZƒ‹‚ًڈWگد‚µ‚½چإگV‚جFPGAپuVirtex UltraScale VU440پv‚جڈo‰×‚ًژn‚ك‚½پBژںگ¢‘مASIC‚ ‚é‚¢‚حSoC‚جƒvƒچƒgƒ^ƒCƒsƒ“ƒO‚ب‚ا‚ج—p“r‚ةŒü‚¯‚éپB

پ@ƒUƒCƒٹƒ“ƒNƒX‚ح2015”N1ŒژپA20nmƒvƒچƒZƒX‹Zڈp‚ً—p‚¢400–œƒچƒWƒbƒNƒZƒ‹‚ًڈWگد‚µ‚½چإگV‚جFPGAپuVirtex UltraScale VU440پv‚جڈo‰×‚ًژn‚ك‚½‚ئ”•\‚µ‚½پBژںگ¢‘مASIC‚ ‚é‚¢‚حSoC‚جƒvƒچƒgƒ^ƒCƒsƒ“ƒO‚ب‚ا‚ج—p“r‚ةŒü‚¯‚éپB

پ@VU440‚حپA5000–œˆبڈم‚جASICƒQپ[ƒg‚ة‘ٹ“–‚µپA‹£چ‡گ»•i‚ة”ن‚ׂؤ4”{‚جڈWگد“x‚ًژہŒ»‚µ‚ؤ‚¢‚éپBƒ†پ[ƒUپ[I/Oگ”‚ح1456’[ژq‚ً”ُ‚¦‚ؤ‚¢‚éپBƒoƒbƒNƒvƒŒپ[ƒ““®چى‚ة‘خ‰‰آ”\‚ب48Œآ‚ج16.3Gƒrƒbƒg/•bƒgƒ‰ƒ“ƒVپ[ƒo‚âپA89Mƒrƒbƒg‚جƒuƒچƒbƒNRAM‚ب‚ا‚à“à‘ ‚µ‚½پB‚±‚جڈWگد“x‚حپAŒ»چs‚جVirtex-7 2000T‚ة”ن‚ׂؤ2”{ˆبڈم‚ج‹K–ح‚ة‚ب‚é‚ئ‚¢‚¤پB‚ـ‚½پAASIC‚ئ“¯—l‚بƒNƒچƒbƒNƒAپ[ƒLƒeƒNƒ`ƒƒ‚ج“±“ü‚âپAچإگV‚ج”zگü‹Zڈp‚¨‚و‚ر—ک—pŒّ—¦‚جچ‚‚¢ƒچƒWƒbƒNƒuƒچƒbƒN‚جچج—pپA‚ئ‚¢‚ء‚½“ء’·‚ً”ُ‚¦‚ؤ‚¢‚éپB

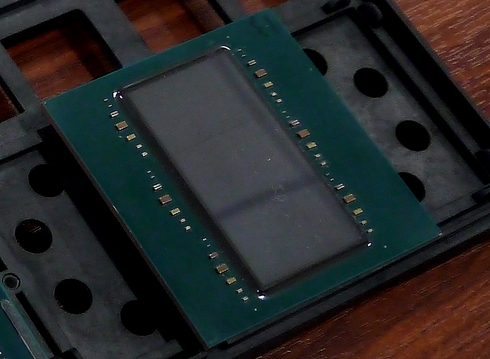

پ@VU440‚حپATSMC‚ج‘و2گ¢‘مSSIپiƒXƒ^ƒbƒNƒh ƒVƒٹƒRƒ“ ƒCƒ“ƒ^پ[ƒRƒlƒNƒgپj‹Zڈp‚ً—p‚¢‚ؤ—تژY‚·‚éپBCoWoSپiChip-on-Wafer-on Substrateپj3D ICƒvƒچƒZƒX‚إچ\’z‚µ‚½SSI‹Zڈp‚حپA28nmƒvƒچƒZƒX‚إ‚·‚إ‚ة—تژY‚جژہگر‚ھ‚ ‚éپB20nmƒvƒچƒZƒX‹Zڈp‚ً—p‚¢‚é‘و2گ¢‘مSSI‹Zڈp‚حپA‚و‚è‘ه‹K–ح‚ب‰ٌکH‚ًپAڈ¬‚³‚¢ƒ`ƒbƒvƒTƒCƒY‚ةڈWگد‚·‚邱‚ئ‚ھ‚إ‚«‚éپB‚ـ‚½پA28nmگ»•i‚ة”ن‚ׂؤپAƒ_ƒCٹش‚ًگع‘±‚·‚é‘رˆو•‚ً5”{‚ةچL‚°‚½‚ظ‚©پAƒXƒ‰ƒCƒX‹«ٹE‚ً’´‚¦‚½ƒNƒچƒbƒLƒ“ƒOƒAپ[ƒLƒeƒNƒ`ƒƒ‚ة‘خ‰‚µ‚½‚±‚ئ‚©‚çپAچ‚گ«”\‚إ’لڈء”ï“d—ح‚جSoC‚ًژہŒ»‚·‚邱‚ئ‚ھ‚إ‚«‚é‚ئ‚¢‚¤پB

Copyright © ITmedia, Inc. All Rights Reserved.

ٹضکA‹Lژ–

ƒUƒCƒٹƒ“ƒNƒX‚ھ28nmFPGAپuArtix-7پv‚ةژشچع‘خ‰•i‚ً’ا‰ءپAپuZynqپv‚ً•âٹ®

ƒUƒCƒٹƒ“ƒNƒX‚ھ28nmFPGAپuArtix-7پv‚ةژشچع‘خ‰•i‚ً’ا‰ءپAپuZynqپv‚ً•âٹ®

ƒUƒCƒٹƒ“ƒNƒX‚حپAژشچعIC‚ج•iژ؟‹Kٹi‚إ‚ ‚éAEC-Q100‚ةڈ€‹’‚·‚éFPGAگ»•iŒQپuXA FPGAپv‚ةپAپuXilinx 7ƒVƒٹپ[ƒYپv‚ج’†‚إ‚àƒRƒXƒg‚ئڈء”ï“d—ح‚ً’ل‚—}‚¦‚½‚±‚ئ‚ً“ء’¥‚ئ‚·‚éپuArtix-7پv‚ً’ا‰ء‚µ‚½پB ƒUƒCƒٹƒ“ƒNƒXپA20nmƒvƒچƒZƒXچج—pFPGA‚جƒTƒ“ƒvƒ‹ڈo‰×‚ًٹJژn

ƒUƒCƒٹƒ“ƒNƒXپA20nmƒvƒچƒZƒXچج—pFPGA‚جƒTƒ“ƒvƒ‹ڈo‰×‚ًٹJژn

ƒUƒCƒٹƒ“ƒNƒX‚ح11Œژ11“ْپi•ؤچ‘ژٹشپjپA‘نکp‚جTSMC‚ج20nmƒvƒچƒZƒX‚ًچج—p‚µ‚½FPGAگ»•i‚جڈ‰ٹْƒTƒ“ƒvƒ‹‚ًڈo‰×‚µ‚½‚ئ”•\‚µ‚½پBˆê”تŒع‹qŒü‚¯ƒTƒ“ƒvƒ‹‚جڈo‰×‚ح2014”N1پ`3Œژ‚©‚çٹJژn‚·‚éپB![FPGAپuArtix-7پv‚جگفŒvگ¶ژYگ«‚ًچ‚‚ك‚é•]‰؟ƒLƒbƒg‚ھ—ک—p‰آ”\‚ة](https://image.itmedia.co.jp/edn/articles/1302/19/news095.jpg) FPGAپuArtix-7پv‚جگفŒvگ¶ژYگ«‚ًچ‚‚ك‚é•]‰؟ƒLƒbƒg‚ھ—ک—p‰آ”\‚ة

FPGAپuArtix-7پv‚جگفŒvگ¶ژYگ«‚ًچ‚‚ك‚é•]‰؟ƒLƒbƒg‚ھ—ک—p‰آ”\‚ة

AC701‚حFPGAپuArtix-7پv—p‚ج•]‰؟ƒLƒbƒg‚إ‚ ‚éپB“¯•]‰؟ƒLƒbƒg‚ًٹˆ—p‚·‚邱‚ئ‚إپAArtix-7‚ًژg‚ء‚½ƒVƒXƒeƒ€‚جٹJ”‚ئŒںڈط‚ًŒّ—¦‚و‚چs‚¤‚±‚ئ‚ھ‚إ‚«‚éپB ƒUƒCƒٹƒ“ƒNƒX‚ھ400Gb ƒCپ[ƒTƒlƒbƒg‚ج“®چىƒfƒ‚‚ًŒِٹJپ\پ\20nmFPGA‚إ

ƒUƒCƒٹƒ“ƒNƒX‚ھ400Gb ƒCپ[ƒTƒlƒbƒg‚ج“®چىƒfƒ‚‚ًŒِٹJپ\پ\20nmFPGA‚إ

XilinxپiƒUƒCƒٹƒ“ƒNƒXپj‚ح2014”N11ŒژپAƒGƒ“ƒWƒjƒAƒٹƒ“ƒOƒTƒ“ƒvƒ‹پiESپjڈo‰×’iٹK‚ة‚ ‚é20nmƒvƒچƒZƒX‚ً—p‚¢‚½FPGAپuVirtex UltraScaleƒtƒ@ƒ~ƒٹ XCVU095پv‚ًژg—p‚µ‚½400Gƒrƒbƒg ƒCپ[ƒTƒlƒbƒg‚ج“®چىƒfƒ‚‚ًŒِٹJ‚µ‚½پB ƒUƒCƒٹƒ“ƒNƒXپA20nmƒvƒچƒZƒXFPGA‚ًƒeپ[ƒvƒAƒEƒgپ\پ\گ»•iگي—ھ”½‰f‚µŒؤڈج‚àپu8پv‚إ‚ح‚ب‚پuUltraScaleپv

ƒUƒCƒٹƒ“ƒNƒXپA20nmƒvƒچƒZƒXFPGA‚ًƒeپ[ƒvƒAƒEƒgپ\پ\گ»•iگي—ھ”½‰f‚µŒؤڈج‚àپu8پv‚إ‚ح‚ب‚پuUltraScaleپv

ƒUƒCƒٹƒ“ƒNƒX‚حپA20nmƒvƒچƒZƒX‹Zڈp‚ً—p‚¢‚½FPGA‚جƒeپ[ƒvƒAƒEƒgپiگفŒvٹ®—¹پj‚ً”•\‚µ‚½پB“¯ژ‚ةپA20nmƒvƒچƒZƒXچج—pFPGA‚ب‚ا‚ة“K—p‚·‚éگVگ¢‘مƒAپ[ƒLƒeƒNƒ`ƒƒپuUltraScaleپv‚جٹT—v‚àŒِ•\‚µ‚½پBگVƒvƒچƒZƒXپAگVƒAپ[ƒLƒeƒNƒ`ƒƒ‚ًچج—p‚µ‚½گ»•i‚جڈo‰×‚ح2013”N10پ`12Œژ‚ً—\’肵‚ؤ‚¢‚éپB