RMS位相ジッタ・バジェットにおけるマージンを拡大する方法:複数の周波数/出力に対応するデバイスで簡単に(1/3 ページ)

周波数マージニングを使ってテストを行うことで、システムの設計余裕度を確認し、その信頼性と堅牢性を最高のレベルにまで高めることができます。

クロック・ジッタは多くの組み込み技術者から「動くターゲット」と呼ばれています。システム設計者や組み込み設計者は、ジッタと、それが設計に及ぼす悪影響について追究し続けています。そうした設計者らは、ジッタを大幅に低減する適切な解決策を見いだしたいと考えています。

システムのデータレートは高まり続け、タイミングに関する要件もますます厳しくなっています。そのため、ジッタへの対処は以前にも増して難易度の高い課題となりました。結果として、組み込み設計者は、クロックICなどについてRMS(Root Mean Square:二乗平均平方根)位相ジッタがなるべく小さいものを求めるようになりました。また、最近では電池駆動式のアプリケーションが急増しました。そうしたアプリケーションでは、RMS位相ジッタを抑えつつ、確実に消費電力を最小化するために、細心の注意を払ってクロックICなどのデータシートを確認しなければなりません。

RMS位相ジッタは通信システムのクロック品質を表す測定項目の1つです。ここで、システム設計者/組み込み設計者がイーサネットやPCI Express(以下、PCIe)といった一般的なプロトコルを使用するケースを考えます。それらの規格では、クロック品質を表す仕様としてRMS位相ジッタの値が定められています。そのため、クロックICなどがPCIeなどの規格を満たしているか否かを判定する際には、RMS位相ジッタを1つの指標にすることになります。

エンドポイントについても考慮しなければなりません。全てのエンドポイントにはジッタについてそれぞれに異なる要件があります。例えば、エンドポイントがPCIeである場合、PCIeのジッタ要件(PCIe Gen3のコモン・クロック方式の場合で1p秒)を満たす必要があるということです。

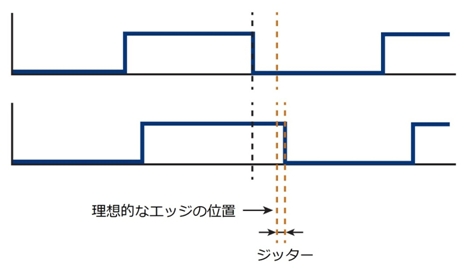

ジッタについては、RMS位相ジッタ以外にもさまざまな指標によって定義されます。ただ、クロック・ジッタの場合、一般に理想的なクロック・エッジの位置からのずれとして定義されます(図1)。

ジッタはシステムのタイミング・バジェットにおいて重要な意味を持ちます。そのため、ジッタに対処して値を最小化するのは非常に重要なことです。今日のシステム・アプリケーションは、従来の設計ノウハウとは異なる先端技術を導入しなければ成り立たないものとなっています。そうしたアプリケーションにおける厳しい要求に応えるためにも、ジッタ対策は非常に重要な課題になっています。

残念ながら、ジッタに対処するためにICとして提供される多くの技術は、最新のアプリケーションにおける厳しい要求に対応できるレベルには達していないでしょう。ジッタの最小化に関してシステム設計者が大きな問題として挙げるのは、許容レベルを超える消費電力と、大きすぎるパッケージ/複数個に及ぶパッケージです。プリント回路基板の小型化が求められる中、経験豊富な組み込み設計者は、単一の小型パッケージで提供されるICによって設計上の基本的な要件に対応したいと考えています。

Copyright © ITmedia, Inc. All Rights Reserved.