RMS位相ジッタ・バジェットにおけるマージンを拡大する方法:複数の周波数/出力に対応するデバイスで簡単に(2/3 ページ)

周波数マージニングを使ってテストを行うことで、システムの設計余裕度を確認し、その信頼性と堅牢性を最高のレベルにまで高めることができます。

“スイート・スポット”が重要

特にモバイル・アプリケーションが急増していることもあって、パッケージの小型化は各種機能の実現に次いで強く求められる要件となっています。しかし、設計者が要求することはそれだけではありません。例えば、ミッドレンジの産業用クロック・ジェネレータが必要になった場合、消費電力と性能の観点から見て“スイート・スポット”に当たる製品が選ばれることになります。実際、1GHz〜10GHzのイーサネット・アプリケーションをサポートし、システムのRMS位相ジッタの要件を全て満たすことで、設計者の全体的な目標に対応可能な製品が登場しつつあります。

ミッドレンジの製品の他に、消費電力とジッタ性能のトレードオフを考慮して実現されたハイエンド/ローエンドのクロック・ジェネレータも存在します。RMS位相ジッタの要件がさほど厳しくないクロック・システムでは、ローエンドのクロック・ジェネレータを使用することができます。一方、10/40/100GbE(ギガビットイーサネット)やファイバー・チャネル向けに非常に低ジッタのクロックを供給するために、消費電力はローエンド/ミドルエンド品より多いものの、ジッタを300f秒以下にまで抑えたハイエンドのクロック・ジェネレータも存在します。

周波数マージニング機能の提供

もう1つ、組み込み設計者が求める要件として周波数マージニング機能が挙げられます。組み込み設計者にとって、システムの信頼性と堅牢性を高めるのは非常に重要なことです。あらゆる設計パラメータの評価を行い、仕様で定められた特定の要件を満たしたうえで、さらにその仕様に対するマージンを確保できるように取り組みます。

このような観点から、ほとんどの設計者はRMS位相ジッタの要件として1p秒以下の性能を求めます。実際、1/10GbEアプリケーションでは、RMS位相ジッタの目標値を1p秒に設定する場合がほとんどです。ところが、市販の多くのクロック・ジェネレータは、RMS位相ジッタの性能として1p秒という値を達成できていません。

そうした製品を採用したのでは、システムの仕様に対して十分なマージンを確保できていないことになります。その一方で、12kHz〜20MHzの積分範囲で0.7p秒という優れたRMS位相ジッタ性能を実現しているプログラマブル・クロック・ジェネレータも存在します。このクロック・ジェネレータを採用したとすると、システムの仕様に対して30%のマージンを確保できることになります。これであれば、信頼性が高く堅牢なシステムを実現することが可能です。

IDT社をはじめ主要な半導体メーカーは、新たな水準の周波数マージニングを実現するために、クロック・ジェネレータについて、集積化が可能で革新的なアーキテクチャを採用する方向に進んでいます。特に、周波数マージニングは、より効率的なアプローチを可能にするものです。これを利用すれば、組み込み設計者は、高性能の民生用機器や、ネットワーク機器、産業用機器、コンピュータ機器、医療用電子機器、放送映像機器、データ通信機器などのアプリケーションにおいて、システムの堅牢性を決定するためにクロック周波数を調整することができます。

一般に、従来のクロック・ジェネレータで周波数マージニングを行うには、周波数を変更するために設計者がクロックを次から次へと手作業で変えていくという単調な作業を行わなければなりません。これは時間を浪費する作業だといえます。そのため、最近の組み込み設計者の要求としては、基板面積とジッタの要件を効率的に満たすために、単一のパッケージで数種の出力周波数と数種の出力方式に対応していることが重視されるようになっています。

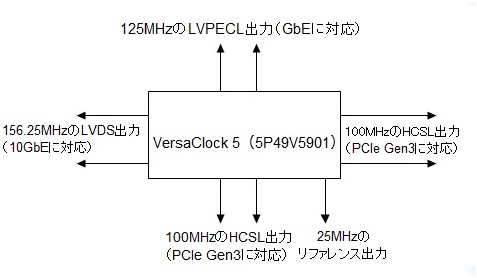

そうしたICの例として、プログラマブル・クロック・ジェネレータ「VersaClock 5(5P49V5901ANLGI)」(IDT)を挙げます(図2)。

このICの出力は、互いに独立した状態で、4種の異なる周波数、4種の異なる出力形式に構成(コンフィギュレーション)することができます。さらに1種のリファレンス・クロックを出力することも可能です。こうした出力機能を1チップに集積し、4mm×4mmのQFN(Quad Flat No-lead)という小型のパッケージを採用しています。

4系統のユニバーサル出力ペアは、それぞれHCSL(High-Speed Current Steering Logic)、LVPECL(Low Voltage Positive Emitter Coupled Logic)、LVDS(Low Voltage Differential Signaling)、または2本のLVCMOS(Low Voltage CMOS)に構成できます(図3)。

| 出力周波数 | 出力形式 | RMS位相ジッタの積分値 (12kHz〜20MHz) |

|---|---|---|

| 100MHz (PCIe Gen3に対応) |

HCSL | 754f秒 |

| 125MHz (イーサネットに対応) |

LVPECL | 700f秒 |

| 156.25MHz (10GbEに対応) |

LVDS | 769f秒 |

| 100MHz (PCIe Gen3に対応) |

HCSL | 751f秒 |

| 25MHz (リファレンス出力) |

LVCMOS | 312f秒 |

| 図3 4系統のユニバーサル出力ペアは、HCSL、LVPECL、LVDS、LVCMOSに構成できる。最大350MHzの異なる周波数出力に対応可能となっている | ||

それぞれ、最大350MHzまでの独立した周波数を出力することが可能です。4種の周波数出力は、1つの水晶振動子またはリファレンス・クロック入力を基に生成され、5MHz〜350MHzの周波数出力はRMS位相ジッタ0.7p秒の性能です。

Copyright © ITmedia, Inc. All Rights Reserved.