ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト:SoCの低消費電力設計ノウハウ(2/4 ページ)

SoCの低消費電力化で見過ごされがちな“インターコネクト”。ここでは、SoCのダイサイズを縮小し、消費電力を低減できるモジュール方式のSoCインターコネクト技術について紹介する。

バスとクロスバー:インターコネクトの歴史

インターコネクトファブリックの歴史は、モジュール型NoC設計の考えがどのように生まれ、拡張性の問題をどう解決しているのかを示しています。

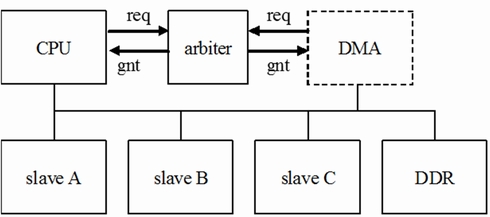

SoCはCPUとペリフェラルを搭載したチップであり、開発者はこの2つの要素を結ぶためのインタフェースプロトコル標準を策定しました。さらにバスマスタの出現により、ペリフェラルへの接続が共有されました。バスアクセスの制御には、基板レベルのプロトコルで使用されているようなセントラルアービタが必要でした。

時間の経過とともにSoC設計者はIPコアの数をどんどん増やしていきました。設計の複雑さが増すにつれ、必要とされるバスインタフェースの数も増えていきました。このためチップ上の処理量が増大すると、異なるバスマスタが異なるスレーブに対して処理を要求している場合でさえ、バスへのアクセスにかなりの待機時間が発生し得ました。

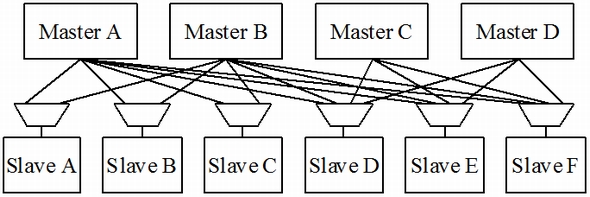

待機時間による遅延を解消するために、インターコネクト内の複数のマスタとスレーブ間の同時アクセスを可能にするクロスバースイッチが開発されました。以下の論理図は、4つのマスタが4つの異なるスレーブに対して4つの同時トランザクションを実行している様子を示しています。

物理的に、クロスバースイッチは各スレーブでマルチプレクサとともに実装されます。各マルチプレクサは分散アービトレーション方式でアービタと結合されます。

この方式でマスタとスレーブのインタフェースの数を増やしていくことができます。ただし一定の数を超えると、SoC全体に全てのデータパスをルーティングするときのサイズが場所と経路の面で現実的ではなくなります。

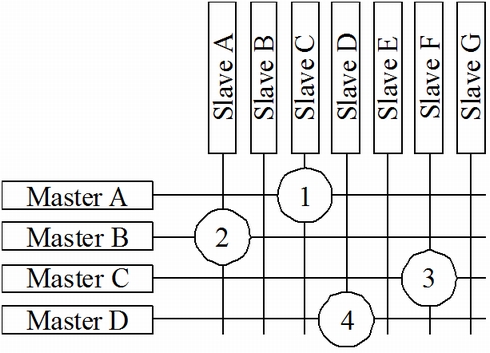

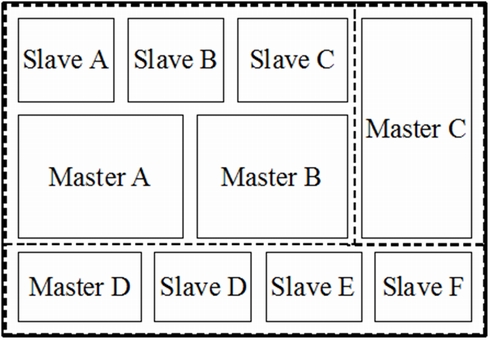

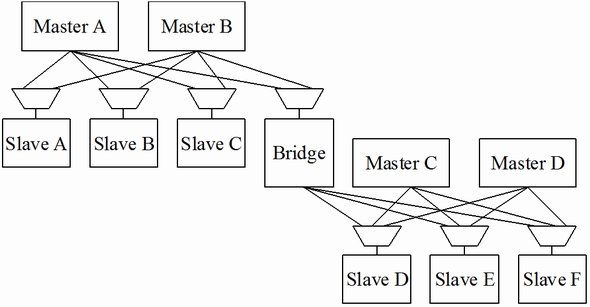

マスタ/スレーブ間インタフェースの数が多い複雑なチップの場合、IPコアグループの配置に従って、複数の物理領域内で個別のインターコネクトを設計する必要があります。領域間をつなぐブリッジがマスタ/スレーブ間に必要な接続を供給します。

ブリッジがロジック遅延オーバーヘッドをホールドし、データトランザクションに遅延サイクルを追加します。

クロスバーインターコネクトは、同時アクセスが招くシステムアーキテクチャ上の問題を解消するが、マスタとスレーブのIPブロック数が多いチップでは物理的な実装上の問題が生じます。

Copyright © ITmedia, Inc. All Rights Reserved.