ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト:SoCの低消費電力設計ノウハウ(3/4 ページ)

SoCの低消費電力化で見過ごされがちな“インターコネクト”。ここでは、SoCのダイサイズを縮小し、消費電力を低減できるモジュール方式のSoCインターコネクト技術について紹介する。

モジュール設計とNoC

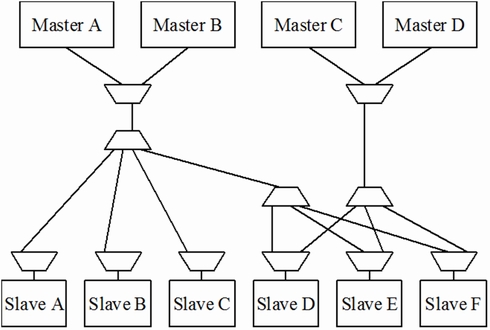

アドレスをマスタインタフェースでデコードし、単純なルートIDに変換することで遅延を短縮できます。アービタ/マルチプレクサとルータ/デマルチプレクサのオンチップネットワークで単純なルートIDを使用し、単純な疑似スイッチマルチプレクサをリンクすることでチップ全体にルーティングを分散できます。これによりインターコネクトロジックの配置を効率化できます。チップ内の配線数が増えるに従ってルーティングを容易にする配置がますます重要になってきています。

前述した2つの問題を解決するNoCインターコネクトは、携帯電話機用アプリケーションプロセッサ、デジタルTVやセットトップボックス用SoCなどの高度な設計で広く使用されるようになってきました。

SoCにより多くのフィーチャを集積することが求められるにつれ、インターコネクト技術への需要が高まってきました。特に需要が高いのは以下のフィーチャです。

- 各種トランザクションプロトコルへのインタフェース

- スイッチ(デマルチプレクサ/ルータ、アービタ/マルチプレクサ)

- QoS(Quality of Service)

- バッファ

- データパスのシリアル化

- 統計プローブ

- デバッグトレース

- ファイアウォール

- レジスタスライス(パイプステージ)

- クロックドメインクロッシング

- 電圧ドメイン

- 電力ドメイン

これらがインターコネクト設計における新たな課題を生んでいます。

設計者はIPを再利用・再構成可能にしたいと思いますが、厳しさが増すフィーチャ要件をクロスバーのロジック内で対応すれば複雑さが生まれ、クリティカルパスの速度低下を招きかねません。さらに、少量のトラフィックに対してさえ多くの配線がトグルされるため、トラフィック量相応の電力よりも大きな電力が消費されます。一方、再利用可能なモジュール型インターコネクト設計は、これまでのバスやクロスバー技術に見られる複雑さをなくすことで、簡潔さ、スピード、面積、電力効率の全ての面で優位性をもたらします。

トランザクション層、伝送層、物理層

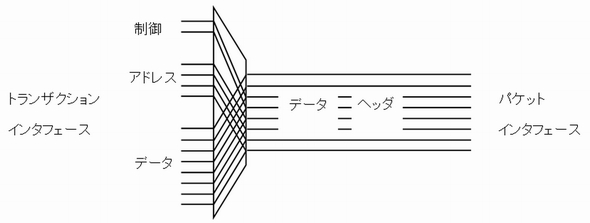

NoC技術はトランザクション層を最上位とする3層プロトコルを用いています。トランザクション層は読み出し/書き込み要求をAMBA、PIF、OCP、あるいは他の業界標準プロトコルを用いて実行します。また、インターコネクトで接続されるIPブロックの設計者にとっての可視インタフェースでもあります。

NoCの伝送層プロトコルはネットワークインタフェースユニット(NIU)によって管理され、これがトランザクションごとに1つ以上のパケットを生成します。全てのパケットにヘッダがあり、読み出しデータパケットと書き込みデータパケットはヘッダの後にデータペイロードを含んでいます。パケットヘッダはアドレス、トランザクションパラメータ、サイドバンドシグナルをフィールドとしてエンコードし、NIUは未解決トランザクションとタグ付きシーケンスを制御します。ヘッダフォーマットは最小限に抑えられており、NoCごとに最適化されます。ヘッダは、イニシエータからターゲットへの要求と、ターゲットからイニシエータへの応答をルーティングするためにインターコネクト内の各疑似スイッチで使用されます。要求パスと応答パスは独立しているため、ロジックとアーキテクチャの従属性がなくなり、デッドロックは生じません。

モジュール型設計により、伝送パケットを非常に単純なプロトコルで物理層に転送することが可能になります。このプロトコルは以下のシグナルで構成されます。

- Data[Nビット](送信側が駆動)

- Valid[1ビット](送信側が駆動)

- Ready[1ビット](受信側が駆動)

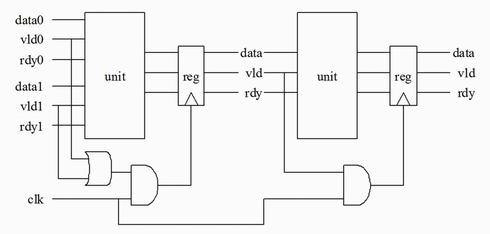

“Valid”と“Ready”でフロー制御が実現されるため、バックプレッシャー・フィードバックが可能になります。この単純なハンドシェイクプロトコルはNoCの全ユニット間に存在します。単純なインタフェースに基づく標準化により、さしずめ子ども用の連結積み木のようにユニットを相互接続できます。

クロックツリーゲーティング

よく知られているチップ設計手法では、トグルが要求されないサイクル中の各フリップフロップでクロックをゲーティングすることが可能であり、どのインターコネクト技術でもフロップに適用できます。しかし、クロックツリーの消費電力の問題は解決されていません。

クロックツリーは単一シグナルです。したがってデータパスよりもはるかに狭いです。しかし、物理的に分散している全てのフロップに到達させるため、クロックツリーには各データパスよりも長い配線が使用されます。定義により、クロックは1クロックサイクルにつき2回トグルするため、クロックツリーは一般的にデータパスよりもはるかに多くの電力を消費します。

クロスバー内では、データが流れていない時と場所でさえ全てのクロックネットがトグルします。クロスバー内のどこにもデータが転送されていないときのサイクルで、全てのクロスバーロジックに対してクロックゲーティングを行うことは理論的には可能ですが、これは現実的ではありません。離れている複数のフロップに対して再びイネーブルシグナルを生成するには、離れている複数のシグナルを処理する大規模なクロックゲーティングマルチプレクサが必要になるでしょう。

組み合わせロジックの最小モジュールからインターコネクトを構築すれば、モノリシックなクロスバー内で実現可能な粒度よりもはるかに微細な粒度でユニットレベルのクロックゲーティングを実現できます。

ユニット内およびユニット間のレジスタは、データトラフィックがあることを示す有効なハンドシェイクシグナルがアサートされた場合にのみトグルされます。ゲーティングロジックは各ユニットにローカルであるため、パスが短くなり、イネーブルシグナルの生成に必要な多重化が最小限に抑えられます。クロックゲーティングは分配されるため、モジュール型インターコネクトの各モジュールは、残りのシステムの状態に関係なく、アイドルクロックサイクル時にゲートオフされます。これにより、ほぼ理想的な最小のスイッチング消費電力が実現されます。

Copyright © ITmedia, Inc. All Rights Reserved.