LDO型リニアレギュレータで実現する定電流源:Design Ideas パワー関連と電源(2/2 ページ)

リニアレギュレータの電圧出力端子とグラウンド端子との間に固定抵抗を挿入すると、簡単に定電流源を構成できる。レギュレータの出力は定電圧であり、抵抗値が固定であれば、その両端を流れる電流は一定となる。今回は、負荷の高電位側にも低電位側にも定電流源を配置できる回路を紹介する。

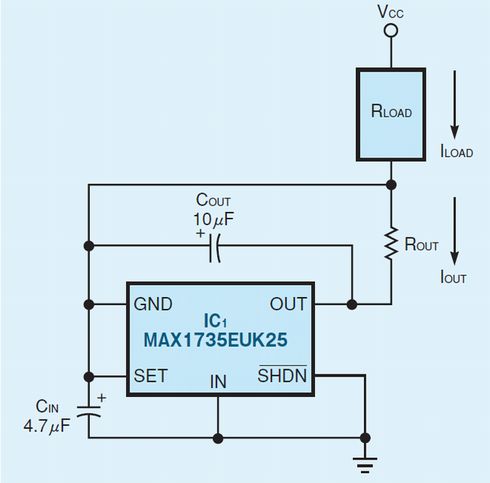

下流側も図1と同様に電位差を設定

次に下流側の定電流源の例を紹介する。図2のように構成することで、負荷抵抗RLOADを介し、2.5V/ROUTの定電流を発生させることができる。この回路で使用している負電圧出力のリニアレギュレータ「MAX1735」(IC1)は、GND端子に対して、2.5V低い電圧を出力する。

図1の場合と同様に、この回路を正常に動作させるには、IC1のIN端子とGND端子の間の電位差を2.5V〜6.5Vに設定する必要がある。つまり、IN端子とGND端子の間の電位差が2.5V〜6.5Vになるように、出力抵抗ROUTの値を選択すればよい。

例えば、VCCを5V、最大負荷を100Ωとしたい場合であれば、ROUTは100Ω以上である必要がある。このとき、最大電流は2.5V/100Ω=25mAとなる。これにより、IN端子とGND端子の間の電位差は、最小値の2.5Vとなる。なお、MAX1735は5端子のSOT23パッケージで提供され、その最大出力電流は200mAである。

図2:下流側用の定電流源回路 (クリックで拡大)

この回路では、図1と同様、2.5V/ROUTの定電流を得ることができる。ROUTの値は、IC1のIN端子とGND端子の間の電位差が2.5V以上になるようなものとする。

静止電流を最小限に抑えるには

ここで紹介した回路では、レギュレータの静止電流が負荷抵抗に流れ、それが誤差の原因となる。この誤差(静止電流)は、レギュレータのIN端子とGND端子の間の電圧によって変化する。従って、静止電流が少ないレギュレータを選ぶか、あるいは動作状態では条件の変動にかかわらず静止電流が一定なレギュレータを選べば、ROUTを調整することで誤差を最小限に抑えられる。

ちなみに、図1の例の場合、レギュレータの静止電流は平均130μA、レギュレータの入力電圧(IN端子)が2.5V〜5Vのときの誤差は40μA未満である。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

電気2重層キャパシタで電池の出力を高める

電気2重層キャパシタで電池の出力を高める

電池で駆動する電子機器は、消費電流の平均値はそれほど大きくない。しかし、瞬間的にでも大きな電流を供給するためには、エネルギーの大きな電池を用意する必要がある。そこで、エネルギー容量の大きな電池を使わなくて済む、電気2重層キャパシタを電池に組み合わせた電源回路を紹介する。 FPGAに向けた電源シーケンス回路

FPGAに向けた電源シーケンス回路

システムを設計する場合、電源投入と電源切断のときに発生する、コア電圧(内部回路に供給する電源電圧)とI/O電圧(入出力回路に供給する電源電圧)のタイミングと、その電圧差に注意を払う必要がある。電源投入/切断時に3.3Vの入力電圧を1.8Vのコア電圧に変換し、I/O電圧は3.3Vを保つようにして、2つの電源電圧の差を最小に抑える回路を紹介する。 リニア・レギュレーターを低コストDC-DCコンに

リニア・レギュレーターを低コストDC-DCコンに

高効率の電源を必要とするものの、高価なDC-DCコンバータICを使いたくない技術者に向けて、リニア・レギュレーターを使った安価なDC-DCコンバータを紹介する。 昇圧型レギュレーターに降圧動作を追加する

昇圧型レギュレーターに降圧動作を追加する

SEPICレギュレータには、変換効率や磁性部品の点で欠点がある。そこで、SEPICレギュレータの代わりとして使える回路を提案する。