USB 3.1/Type-Cの概要と測定の肝:USB Type-Cの登場で評価試験はどう変わる?(1)(4/4 ページ)

高速伝送や電力供給(PD:Power Delivery)機能をサポートするUSB 3.1およびType-Cが登場し、注目を集めている。USB 3.1およびType-Cコネクタを搭載した機器を開発するに当たって、システム設計者が知っておくべき試験/評価方法について解説する。

USB 3.1 / Type-C搭載の製品開発における課題とは?

これまで解説してきたように、USB 3.1/Type-Cではこれまでにはないユニークな特長がある。10Gbpsの超高速伝送の実装、複数の伝送規格の乗り入れとオルタネートモードを使った切り替え、最大100Wまでの電源供給、リバーシブル接続可能にするコネクタ形状と24ピンの高密度実装などである。

ここで、課題として挙げられるのは、物理層開発である。10Gbpsもの超高速伝送を、場合によっては1m以上離れた距離で実現する必要があるが、そのためには高周波信号を取り扱うノウハウが必須となる。基板レイアウトや部品選定、イコライザやディエンファシスなどの信号補正技術の活用が肝となってくる。また、オルタネートモードではスイッチを介して信号パスを切り替えるが、それらの切り替えスイッチ部における信号劣化なども懸念事項の1つである。

また、最大100Wまでの電源供給を取り扱う点においては、突入電流や負荷変動ノイズなどもより注意して扱う必要がある。リバーシブル接続における両面の電気的評価と、高密度実装で懸念される隣接信号ライン同士のクロストークによる信号品質劣化も大きな課題となる。リンク層/プロトコル層も課題だ。電源仕様をネゴシエーションする際のCCラインのプロトコルのやり取りや、オルタネートモード時のスイッチ動作とチップコントローラの連携など、リンク層/プロトコル層の実装もより複雑化していくことが予想される。

試験/評価方法はより高度で煩雑に

USB 3.1/Type-Cコネクタは、PCや携帯端末をはじめとして、その応用市場は極めて大きいと予想されている。それだけにシステム開発や性能評価、相互接続性などに対する試験が重要となる。特に物理層課題に対して、基板設計が製品ごとに異なり多岐にわたるため、相互接続性への懸念は大きい。製品がUSB規格に準拠しているかどうかを、適切なテスト方法で評価していくことが重要となる。その試験/評価方法について詳細な解説は次回以降に行うこととし、ここでは、その概略について述べる。

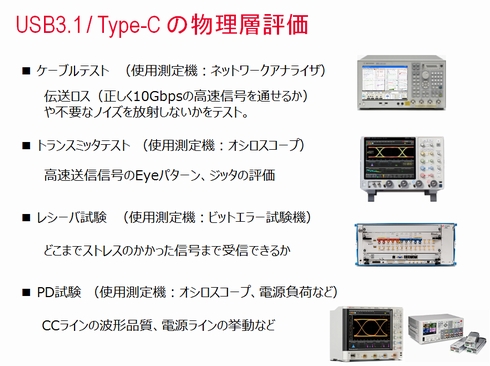

USB 3.1/Type-C規格に関連した試験を大別すると「ケーブルテスト」、「トランスミッタテスト」、「レシーバテスト」および「PDテスト」がある。「ケーブルテスト」では、ケーブルが正しく10Gbpsの高速信号を通せるか、不要なノイズを放射しないかをテストする。「トランスミッタテスト」、「レシーバテスト」は、ホスト/デバイス機器の物理層の試験で、10Gbps信号波形のジッタやアイパターンの試験と、レシーバのジッタ耐性試験が行われる。「PDテスト」は、CC端子の波形品質や、PD通信プロトコルのチェックおよび電源供給能力の試験が行われる。

特に、USB 3.1/Type-C規格は、伝送速度や給電の範囲が広い。しかもコネクタは上下の向きを気にせずに利用可能にしたことなどから、これまでに比べてチェックすべき機能/項目は増加し、一段と煩雑になっている。相互接続性を保証するためには、USB-IF(Implementers Forum)が定めるコンプライアンス試験に合格する必要がある。

次回より、高性能オシロスコープやネットワークアナライザ、自動コンプライアンス試験ソフトウェアなどを用いた、USB 3.1/Type-C規格の試験/評価方法などを、より詳しく紹介する。

(第2回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

これから世界を席巻する!? USB Type-Cを知る

これから世界を席巻する!? USB Type-Cを知る

これから、世界を席巻するであろう新しいコネクタ『USB Type-C』(USB-C)。USB前夜や歴代USBコネクタを振り返りながら、素晴らしいUSB Type-Cを紹介していこう。 ついにやってきたUSB Power Delivery(USB PD)とは

ついにやってきたUSB Power Delivery(USB PD)とは

USB Power Delivery(USB PD)をご存じでしょうか? 100Wまでの給電を全てUSBケーブルで行ってしまうという新しいUSB規格。既にUSB PDの仕組みを搭載したPCも発売されています。ここでは、あらゆる機器の給電スタイルを一新する可能性のあるUSB PDがどのような規格で、どんなことができるかなどを解説していきます。 USB3.1 Gen2の高速データレート“10Gbps”で変わったテスト要件

USB3.1 Gen2の高速データレート“10Gbps”で変わったテスト要件

3回にわたって、最新USB規格である「USB3.1」に対応するための試験について解説していく。第1回は、10Gビット/秒の高速データレートに対処するための課題を洗い出しながら、トランスミッタとレシーバのプレコンプライアンス試験の概要を紹介しよう。 知っておきたいUSB3.0まとめ

知っておきたいUSB3.0まとめ

USB2.0に比べてデータ伝送速度が約10倍になった新しい通信規格USB3.0。今回は、このUSB3.0について解説します。