32/64bitを追加した高性能MIPS Warrior CPU:イマジネーション・テクノロジーズ

イマジネーション・テクノロジーズは、MIPS Warrior CPUのラインアップに、組み込み32ビットMクラスCPU「M6200」「M6250」と64ビットPクラスCPU「P6600」を追加した。

イマジネーション・テクノロジーズは2015年11月、MIPS Warrior CPUのラインアップに、組み込み32ビットMクラスCPU「M6200」「M6250」と、64ビットPクラスCPU「P6600」を追加したと発表した。

M6200/M6250は、MクラスファミリのMCU/MPU用プロセッサの最新製品である。有線/無線モデム、GPU制御プロセッサ、フラッシュおよびSSDコントローラ、パケット処理、モータ制御、音声処理など、高い性能と広いアドレス空間を必要とする分野の高性能組み込み設計に対応する。

優れた演算処理性能と面積効率

6ステージパイプラインを実装し、MIPS microAptiv CPUよりも30%高い周波数で動作する。DSPおよびSIMD機能を内蔵し、アプリケーションの信号処理要件に対応。また、microMIPS r6命令セット・アーキテクチャ(ISA)をサポートし、優れたコード圧縮率とコンパクトなメモリフットプリントを可能にした。ECCとパリティ保護を含むデータ整合機能、AMBA APBデバッグ・インタフェースを備えるため、JTAG、マルチコア、ミックストコアのデバッグができるという。

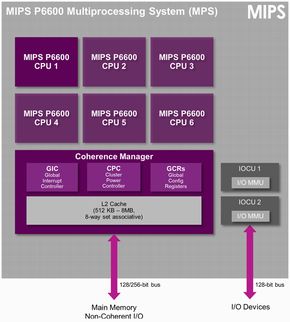

P6600は、16ステージマルチイシューアウトオブオーダー(OoO)パイプラインを実装した高性能64ビットCPUで、優れた演算処理性能と面積効率が特長。32ビットP5600CPUを基に開発され、128ビット MIPS SIMDアーキテクチャ(MSA)をサポートすることで、マルチメディアアプリケーションのベクトル演算を効率的に並列処理できる。フルアソシアティブレベル1 BTB(分岐ターゲットバッファ)と改良されたレベル2 キャッシュサブシステムを備え、洗練された分岐予測を可能にした。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

低電力通信プロトコルをサポートする開発環境

低電力通信プロトコルをサポートする開発環境

NXPセミコンダクターズは、ARM mbed OS上で動作する「NXP Threadプラットフォーム」を発表した。ワイヤレスマイクロコントローラを採用し、ZigBee3.0/Threadなどの低電力通信プロトコルをサポートする。 144端子品を追加、車載制御向け16bitマイコン

144端子品を追加、車載制御向け16bitマイコン

ルネサス エレクトロニクスの「RL78/F15」は、消費電力が小さい16ビットマイコンである。BCM(ボディ制御モジュール)や車載エアコン、パワーシートといった車載制御システムの用途に向ける。 Wi-Fi通信機能を内蔵したHDR対応のSTB向けSoC

Wi-Fi通信機能を内蔵したHDR対応のSTB向けSoC

STマイクロエレクトロニクスは、Wi-Fi通信機能を内蔵した、セットトップボックス(STB)向けのSoC「Cannes Wi-Fi(STiH390)」を発表した。6K DMIPSのマルチコアARM CPUとWi-Fi 802.11ac 4x4を搭載し、HDRに対応している。 CPUコアから独立動作する周辺モジュール内蔵PIC

CPUコアから独立動作する周辺モジュール内蔵PIC

Microchip Technologyの「PIC16F18877」と「PIC16F1579」は、CPUコアから独立して実行することができる周辺モジュール(CIP)を内蔵した8ビットPIC MCU(マイクロコントローラ)ファミリである。IoT(モノのインターネット)機器、ウェアラブル機器などの用途に向ける。