ニューラルネットワーク向けビジョンプロセッサ:ケイデンス テンシリカVision P6 DSP

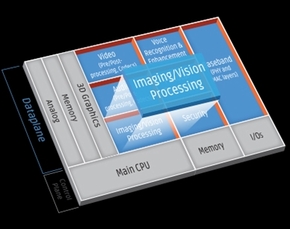

ケイデンス・デザイン・システムズは、組み込み機器向けのニューラルネットワークアプリケーションを対象にしたイメージングプロセッサ「テンシリカVision P6 DSP」を発表した。

ケイデンス・デザイン・システムズは2016年5月、組み込み機器向けのニューラルネットワークアプリケーションを対象にした、高性能ビジョン/イメージングプロセッサ「テンシリカVision P6 DSP」を発表した。

積和演算性能が4倍向上

テンシリカVision P6 DSPは、前バージョンのVision P5 DSPに比べ、畳み込みニューラルネットワークアプリの性能を左右する積和演算性能が4倍に向上した。コンピュータビジョンの鍵となる畳み込み/FIRフィルター/行列乗算などの機能に対しては、8ビットと16ビット演算を利用することで、パフォーマンスが最大で4倍向上するとしている。

また、標準的なニューラルネットワークの実装では、一般的に利用されている各種GPUより低消費電力で、2倍のフレームレートを可能にしている。オンザフライのデータ圧縮を実装するため、高いパフォーマンスが要求されるニューラルネットワークのFCレイヤーに対して、要求されるメモリのフットプリントと帯域幅を大幅に削減できる。

前バージョンのVision P5 DSPとは互換性を備え、オプションとして、IEEE754準拠の半精度浮動小数点FP16を含む32並列のSIMDベクター型浮動小数点ユニットも提供。これにより、浮動小数点演算の性能はVision P5 DSPの2倍に向上し、既存の浮動小数点を使用したニューラルネットワークの設計資産が容易に使用できる。

先行顧客への販売開始は、2016年6月末を予定している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ETXデバイスの寿命延ばすマルチメディアモジュール

ETXデバイスの寿命延ばすマルチメディアモジュール

VIA Technologiesは、組み込み用マルチメディアモジュール「VIA ETX-8X90-10GR」を発表した。ETX規格に準拠し、1.06GHz動作のVIA Eden X1 E-SeriesプロセッサとVIA VX900メディアシステムプロセッサを搭載しているという。 車載設計を簡素化する同期整流昇圧コントローラ

車載設計を簡素化する同期整流昇圧コントローラ

インターシルは、2相55V同期整流昇圧コントローラ「ISL78227」と「ISL78229」を発表した。高出力車載機器の設計を簡素化し、より小型で堅牢な設計を可能にするという。 東芝、ADASの単眼カメラに適した画像認識用LSI

東芝、ADASの単眼カメラに適した画像認識用LSI

東芝は、先進運転支援システム(ADAS)の単眼カメラに適した画像認識用LSI「TMPV7602XBG」を開発したと発表した。安全運転支援で求められる車周辺の歩行者や標識、信号機などの認識を行い、4種類の特徴量を複合特徴量として処理を行うことで夜間でも高精度な画像認識ができるという。 USB Type-C/PD実装を可能にするインタフェースIC

USB Type-C/PD実装を可能にするインタフェースIC

STマイクロエレクトロニクスは、USB Type-CとUSB Power Deliveryの実装を可能にするインタフェースIC「STUSB16」を発表した。設計の柔軟性を向上させ、保護機能を集約できるという。