複数の高速DACを用いたアンテナ・ダイバーシティーによる信号受信の改善:ピコ秒レベルでの同期をとるには?(3/3 ページ)

複数のアンテナを利用してアンテナ・ダイバーシティーを実現する際に、各チャンネルのD-Aコンバーター(DAC)をピコ秒レベルで同期させる必要があります。そこで、高度な同期を図りやすくした高速DACが登場しています。ここでは、アンテナ・ダイバーシティーに必要な要件を整理しながら、そうした新しい高速DACの利点を見ていきましょう。

同期化

DACがギガヘルツ(GHz)の速度でデータを出力する場合、複数のデバイス間で出力を同期させることは極めて困難です。DACが2.7Gサンプル/秒(sps)でサンプリングする場合、出力符号は370ピコ秒ごとに変化します。FPGAのサンプル・クロックとデータ・クロックは、各送信DACについて調整する必要があります。

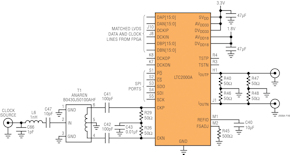

しかし、通過するデータの冗長性を調整できる内部レジスターを備えているDAC(例えば、「LTC2000A」など)であれば、同期化を簡略化することが可能です。なお、この内部レジスター機能を利用するには、各DACのデータ・ラインとクロック・ラインのタイミングのミスマッチをサンプル・クロック周波数の0.4サイクル以内にしなければなりません。

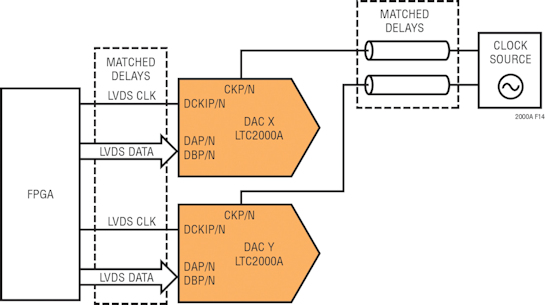

図1に、内部レジスターを備えるLTC2000Aを例に挙げて、2つの理想的なルーティングを示しました。

各DACのデータ・パスとクロック・パスのトレース長は、ピコ秒以内で一致させる必要があります。これは、適切なデジタル・ルーティング・テクニックにより実現します。この条件が満たされれば、デバイス間でのデータの差が1サイクルの範囲内に収まることが保証されます。このDAC内には、データ・パイプラインの冗長性をプログラミングする内部レジスターがあります。各DACレジスターは個別の設定が可能なので、究極的には時間領域の全てのDACを調整することが可能です。これにより、全てのダイバーシティー・テクニックを用いる際のパフォーマンスを最大限に高めることができます。送信側のDACの数が増えれば、ダイバーシティーの可能性も広がります。多くのDACを同期させることができれば、アンテナ・ダイバーシティーが向上し、より大きなアンテナ・アレイが実現します。

まとめ

最先端の無線設計では、パフォーマンスの限界が常に拡大されています。複数のアンテナを利用してアンテナ・ダイバーシティーを実現すれば、これまで直面していたマルチパス・フェージングという問題を解消することができます。LTC2000Aなど内蔵の同期機能を持つDACにより、複数アンテナの実装を可能にします。コントロール・レジスターに若干の修正を加えるだけで、DACをいくつでも同期させることができます。多数のDACを同期させる場合は、1つまたは複数のアンテナを必要とする複雑なビームフォーミング・アプリケーションでの使用が可能です。また、こうしたDACは、時間、周波数、符号といった他のダイバーシティー方式との併用もできます。

【著:Clarence Mayott(クラレンス・マヨット)氏/Linear Technology(リニアテクノロジー)ミックスド・シグナル製品 アプリケーション・エンジニア】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

D-Aコンバータの進化で基地局アーキテクチャはこう変わる

D-Aコンバータの進化で基地局アーキテクチャはこう変わる

無線システムの基地局においては、どのようなアーキテクチャを採用するにしても、D-Aコンバータが必須の構成要素となる。そして、このD-Aコンバータがより高性能のものへと進化することで、アーキテクチャにも大きな変化がもたらされる可能性がある。本稿では、そうした新たなアーキテクチャの1つである「ダイレクトRFコンバージョン」について解説する。 RF回路の設計を簡素に、4G通信やマイクロ波P2P無線向けRF IC

RF回路の設計を簡素に、4G通信やマイクロ波P2P無線向けRF IC

アナログ・デバイセズ(ADI)は、これまで外付けしていたディスクリート素子などの機能を集積することで、RF回路部の設計を簡素化することができるRF IC製品を発表した。I/Q変調器など3製品は、3G/4G通信やマイクロ波によるポイントツーポイント(P2P)無線、防衛/航空宇宙、測定機器などの用途に向ける。 電源システムハードウェアのソフトマネジメント

電源システムハードウェアのソフトマネジメント

プロセッサの電源電圧が1V未満になるなど電源システム設計はより複雑で高度になっている。そうした電源システム設計をより簡便にするデジタルマネジメント技術が登場しているが、出力精度などはアナログマネジメント技術に劣る。そうした中で、デジタル/アナログ双方の長所を生かしたパワーマネジメント技術に注目が集まっている。 期待を背負うIEEE 1588-2008

期待を背負うIEEE 1588-2008

IEEEは、時間同期について定めたIEEE 1588-2008において、時刻と周波数のネットワーク配信に関する規格を大幅に変更した。現在は同規格の活用に向けて、移動体通信の分野で先導的な動きが行われている最中だが、この新しい規格はどのような可能性を秘めているのだろうか。本稿では、IEEE 1588-2008の概要を説明した上で、導入時にポイントとなる事柄や、同規格の将来的な可能性について解説を加える。