DACの精度を改善するためのトリミング:R2RラダーとストリングDAC(1/3 ページ)

高い精度が求められるシグナルチェーンに必須の部品である高精度D-Aコンバーター(DAC)。高精度DACはトリミング(校正)を行うことで、信号精度をさらに高めることができる。本稿では、DACに使われる2つのアーキテクチャ「R2Rラダー」と「ストリングDAC」について説明しながら、両アーキテクチャで精度向上に役立つトリミング手法を検討する。

校正で信号精度を向上

多くの産業用システムが、より高い精度を必要としています。これまで、高精度のシグナルチェーン部品の開発を促進してきたのは、主に計測/テスト機器でした。ですが現在では、ファクトリーオートメーション(FA)、光通信や医療用の機器でも計測/テスト機器同様の“高い精度”を求めています。その中でも、自動テスト装置(ATE)、データ収集(DAQ)や高性能オシロスコープ製品は、最も高精度のシグナルチェーン部品を必要としています。

高精度D-Aコンバーター(以下、DAC)は、このような高い精度が求められるシグナルチェーンに必須の部品であり、高精度信号に最も大きな影響を与える構成要素でもあります。通常、高精度DACは、ゲインとオフセットの微調整や、その他の非直線性を最小にするために使用されます。したがって高精度DACは信号の校正を行うことで、信号の精度を向上することになります。本稿では、DACに使われる2つのアーキテクチャ、R2RラダーとストリングDACについて説明します。さらに、それらのアーキテクチャで精度の向上に役立つ手法を検討していきます。

高精度DACの精度

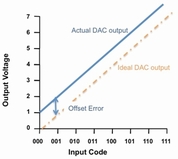

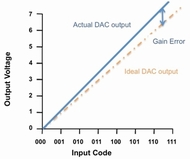

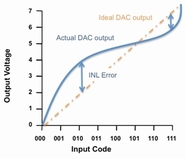

高精度DACを含むアナログICには、数多くの非理想的特性が存在します。高精度DACの直流(DC)誤差の主な原因には、オフセット誤差(OE)、ゲイン誤差(GE)や積分非直線性(INL)があります。オフセット誤差は、図1に示すように、直線動作領域の伝達関数からの、実際の出力値のずれの程度を表します。ゲイン誤差は、図2のように、理想的な伝達関数の傾斜からの偏差を、最下位ビット(1LSB)で表したものです。INLはDACの理想的な出力値と、実際の出力値の間のずれを表します。例として、図3に、簡単な3ビットDACの実際の出力と理想出力の様子を示します。

DACの精度の評価には、これら3種類の誤差の全てが含まれなければなりません。DACの精度を定量的に表すために、しばしば、総合未調整誤差(TUE)という言葉が使われます。これら3種類の誤差は互いに相関していないことから、TUEは式(1)に示すように、これらのニ乗和の平方根(RSS)から計算されます。

オフセット誤差とゲイン誤差は、しばしば、簡単な校正手法を使って、システム上で校正されます。一方、INL誤差の補正には、多くのプログラムコードを使った、より強力な校正手法が必要です。これはソフトウェアにとって無視できない負荷になるとともに、複数の係数を記憶するために、より大きなメモリ容量が必要となります。したがって精度の向上には、DACのINL誤差を最小にすることが最も重要です。

DACのアーキテクチャとINL誤差の関係

最も主要なDACのアーキテクチャはR(抵抗)ストリングまたは、R2Rラダーを使ったトポロジーです。これらの方式のDACで、最も大きなINL誤差の要因となるのは、ラダーやストリングを構成する抵抗のミスマッチです。多くのアナログプロセスは、ラダーやストリングを設計するための高精度抵抗を含みます。より高い精度への要求が増加するにつれて、高精度抵抗では不十分になりました。この問題に対応し、抵抗のミスマッチの影響を補正するために、追加の設計、レイアウトやトリミングなどの追加手法が使われるようになっています。DACの総合的な精度向上に有効な手法は、R2RラダーとRストリングのどちらのアーキテクチャが選択されているかによって異なります。

Copyright © ITmedia, Inc. All Rights Reserved.