DACの精度を改善するためのトリミング:R2RラダーとストリングDAC(2/3 ページ)

高い精度が求められるシグナルチェーンに必須の部品である高精度D-Aコンバーター(DAC)。高精度DACはトリミング(校正)を行うことで、信号精度をさらに高めることができる。本稿では、DACに使われる2つのアーキテクチャ「R2Rラダー」と「ストリングDAC」について説明しながら、両アーキテクチャで精度向上に役立つトリミング手法を検討する。

Rストリング

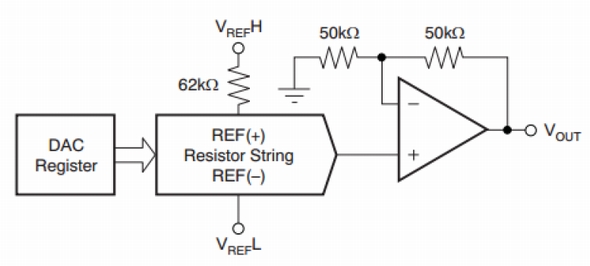

通常、Rストリング方式のDACは、その名前が示す通り、レファレンス電位とグラウンドとの間に抵抗ストリングを接続し、デジタル入力に対応する電圧を発生します。複数のスイッチを介して、この電圧を出力バッファに接続します。出力バッファは、DACにドライブ能力を提供します。例として、図4と図5にRストリングアーキテクチャのDACを示します。

16ビットDACのRストリングには、216個(6万5536個)の抵抗が必要です。通常、Rストリングは最上位ビット(MSB)のストリングと、最下位ビット(LSB)のストリングとして分割されます。それにもかかわらず、INL誤差を最小限にするためには、これら全ての抵抗は、他の抵抗とマッチしていることが必要です。革新的なレイアウト手法のほか、適切なサイズの選択によって、これらの抵抗のマッチングを向上させます。

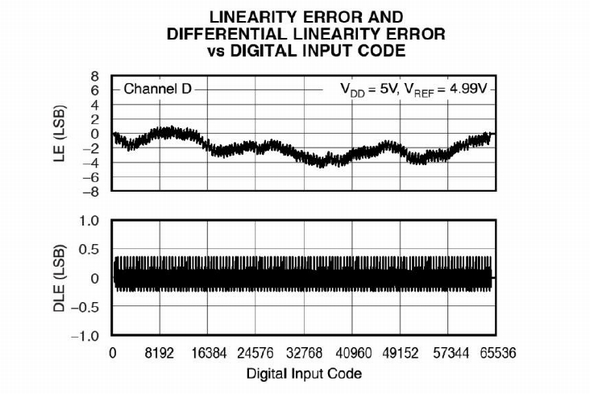

図6に「DAC8554」などのRストリング方式のDACのデジタル入力コードに対するINL特性を示します。

R2Rラダー

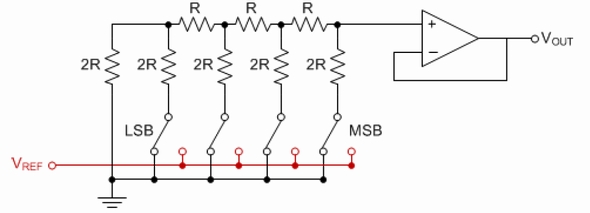

R2Rラダー方式のDACはNビット分解能のDACを最も簡単な形で実装できます。R2RラダーのDACの最も簡単な実装型式はN個の2R抵抗レグと、それらをレファレンス電位(VREF)とグラウンド電位(REFL)に切り替えるスイッチ、1個の2R終端抵抗と、スイッチ付きの2Rレグの間を接続する(N−1)個のR抵抗で構成されています。Nビット分解能のR2Rラダーを構成するには、(3N+1)ユニットのR抵抗が必要です。出力バッファは、必要な負荷ドライブ能力を提供します。このアーキテクチャから明かなことは、このバイナリ重み付きR2Rラダー回路は、分解能1ビットにつき1個のR2Rレグで構成でき、同等のRストリング方式のDACと比較して、抵抗の数を大幅に少なくできるということです。図7に4ビットのR2Rラダー方式のDACの基本回路を示します。

R2R方式のDACの分解能は、回路内の2R抵抗レグの個数で決まります。一方、DACの精度は、抵抗のマッチングによって決まります。回路のLSB側の抵抗レグのミスマッチが精度に与える影響は低く、逆にMSB側になるほどほど、レグのミスマッチは大きな影響を与えるようになります。抵抗レグのマッチング感度の影響は、LSB側からMSB側に向かって、抵抗レグ1段当たり2倍になります。

Copyright © ITmedia, Inc. All Rights Reserved.