モデルベースデザイン手法を使ったProgrammable SoCの協調設計【実践編II】:HDLコード生成から統合検証まで(2/5 ページ)

「モデルベースデザイン手法を使ったProgrammable SoCの協調設計」とはどのようなものか、実践を交えて解説していく本連載。最終回の今回は、実装用モデルによる統合シミュレーションから、HDL/Cコード生成、そして統合検証まで行います。

6.HDLコード生成〜FPGA実装

次はモデルからHDLコード生成を行ってZynqに実装していきます。今回の例では画像処理向けZynq実装用のサポートパッケージを使用してザイリンクス ZC706ボードに実装しています。

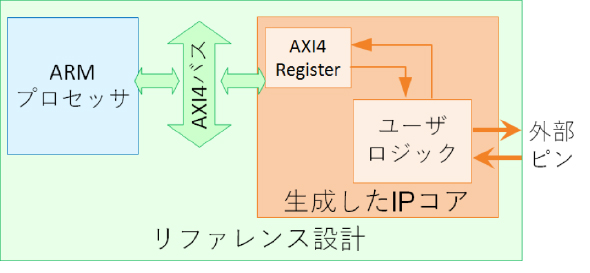

図12に示す実装用モデル中の緑色のサブシステムはFPGA実装用、オレンジ色のサブシステムはプロセッサ実装用となっています。Zynqに実装する手順としては、まずFPGA用サブシステムからユーザーロジックとAXIバスインタフェースを含むIPコアを生成します。ZynqにおけるFPGA用モデル、プロセッサ、レファレンス設計の関係を図12に示します。

IPコアを生成するためには、ターゲットデバイスを指定して実装するためのウィザードであるHDLワークフローアドバイザーを起動します。この画面上には、モデルからFPGAに実装するためのタスクがいくつか並んでいますので、ターゲットのボード、インタフェース、HDLコード生成オプションなどを設定しながら実行していきます。

図13に示すインタフェース設定画面では、ボード定義ファイルであらかじめ登録された外部ピンや、AXI4-Lite、AXI4-Streamバスなどのインタフェースをドロップダウンリストから選択していきます。今回のモデルでは、プロセッサでカルマンフィルターの処理を行うために、検出した座標情報をレジスタベースで読み書きできるAXI4-Liteインタフェースを介して通信しています。その他にもプロセッサからFPGAモデルのパラメーターを変更できるよう接続されているポートはAXI4-Liteに設定します。

タスク3.2ではコード生成が行われます。ユーザーモデルと等価なHDL、AXIバスインタフェースのHDL、IPコア定義ファイル、AXIバスのレジスタアドレスを定義したCヘッダーファイルなど実装に必要なファイル一式が生成されます。

生成したHDLコードのコンパイルは、このHDLワークフローアドバイザーからザイリンクス Vivadoをキックしてバックグラウンドで行われます。最後のタスクまで実行すると、FPGAはプログラムされてアルゴリズムが動作する状態になります。

Copyright © ITmedia, Inc. All Rights Reserved.