モデルベースデザイン手法を使ったProgrammable SoCの協調設計【実践編II】:HDLコード生成から統合検証まで(3/5 ページ)

「モデルベースデザイン手法を使ったProgrammable SoCの協調設計」とはどのようなものか、実践を交えて解説していく本連載。最終回の今回は、実装用モデルによる統合シミュレーションから、HDL/Cコード生成、そして統合検証まで行います。

7.Cコード生成〜プロセッサ実装

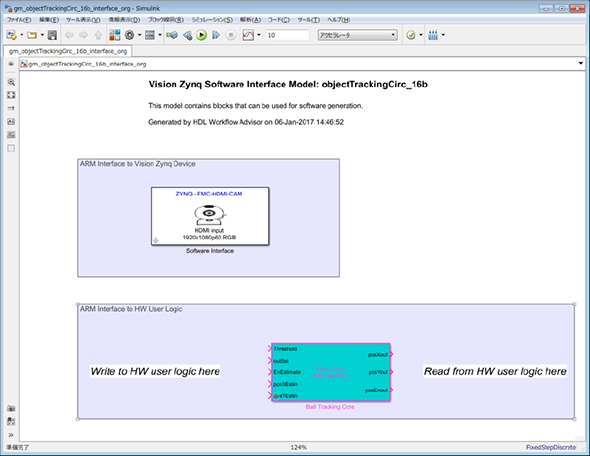

HDLワークフローアドバイザーのタスク4.2 ソフトウェアインタフェースモデルの生成を実行すると、プロセッサに実装するためのモデル(図14)が自動的に生成されます。このモデルには2つのブロックが含まれています。

図14左上に見えるブロックは、サポートパッケージで提供しているターゲットのレファレンス設計のコントロールを行うためにあり、実機の入力ソースやフレームサイズ、フレームレートを設定することができるようになっています。中央下に見えるブロックはプロセッサから見たFPGAに相当するブロックです。このサブシステム内にはAXI4-Liteインタフェースを介して、プロセッサからFPGAに対してデータを読み書きするためのブロックが配置されています。また、ソフトウェアインタフェースモデルでは、HDLワークフローアドバイザーで設定したボードをターゲットにCコード生成を行うよう、コード生成オプションが自動的に設定されています。

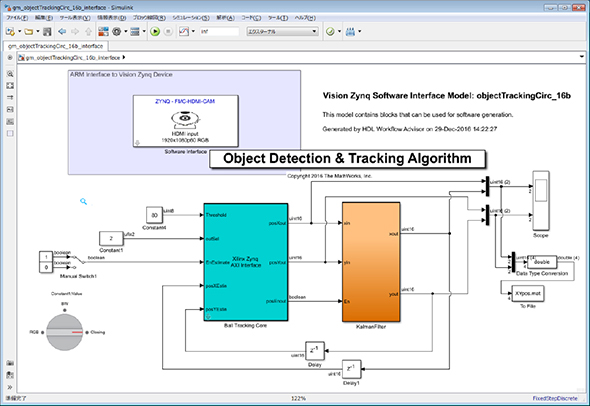

実装モデル(図10)から生成されたソフトウェアインタフェースモデルに、Cコード生成用サブシステムなど必要なブロックをコピーすると、図15に示す、プロセッサ実装用モデルが完成します。

サポートパッケージComputer Vision System Toolbox Support Package for Xilinx Zynq-Based Hardwareは、ARMプロセッサ用のLinuxイメージを提供しており、サポートパッケージインストール時にSDカードに書き込まれます。このSDカードからZynqをブートして、Linux OSが起動した状態でCコード生成を行います。

生成されるコードには、ユーザーモデルと等価なCコード、モデルで設定したサンプル時間での周期タスクで動作するメインコード、AXI4バスに読み書きするデバイスドライバコードが含まれます。続いてザイリンクス SDKをキックしてビルドが行われ、実行ファイルはARMプロセッサにダウンロードされます。実行ファイルはLinux OS上のアプリケーションプログラムとして実行されます。なお、オプションEmbedded CoderでZynqに実装する場合に対応しているOSは、Linux OSの他にVxWorksが対応しています。

Copyright © ITmedia, Inc. All Rights Reserved.