差動信号伝送のメリット ――使用されている技術と注意点:高速シリアル伝送技術講座(2)(2/4 ページ)

高速シリアル伝送技術について基礎から学ぶ本連載。2回目は、差動信号伝送の特徴、メリットに焦点を当て、使用されている技術や注意点について解説していきます。

メリット2)差動信号は波形がきれいで、安定している

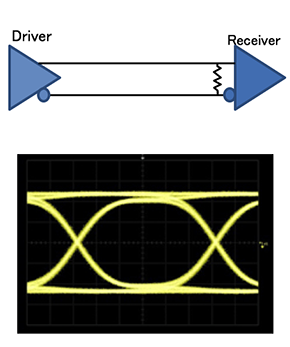

図6-1の波形のように差動信号伝送はリンギングやオーバーシュート、アンダーシュートと呼ばれる反射がなく、CMOS/TTLのシングルエンド信号と比較すると大変きれいな波形となっています。これは差動信号方式と関連はあるのでしょうか?

図6-1は10Gbps差動信号の波形です。差動信号伝送では差動ドライバ、レシーバーのブロック図6-1(上)のように使用する伝送路の特性インピーダンスに合わせた100Ωや90Ωなどの抵抗器をレシーバピンのごく近くに実装(もしくはデバイスに内蔵)しインピーダンスの整合をとります。

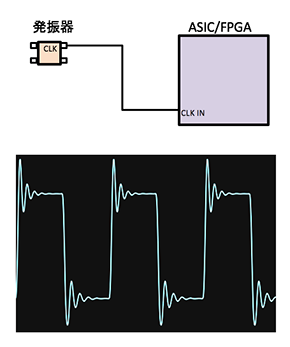

図6-2は一般的なシングルエンド信号の入力端のクロック波形(1.8V振幅 33MHz)ですが、図6-2(上)のブロックの接続のように信号ピンの出力と入力を接続しているだけで、受信端に終端抵抗器は実装されていません。この差から伝送路の特性インピーダンスに合わせた終端抵抗器を置くと、反射のない、きれいな信号伝送ができるのではないかと予想できます。

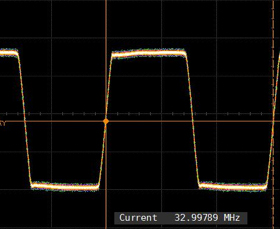

それでは図6-2と同様の1.8V振幅シングルエンド信号と終端器を実装した環境で波形を測定してみましょう。図7は信号発生器とオシロスコープの構成で、送信側は1.8V振幅のクロックを出力し1mの50ΩSMA同軸ケーブルを介して、受信側のオシロスコープに50Ω終端で接続しています。

図8-1はオシロスコープで測定した50Ω終端での1.8V同軸シングルエンド信号33MHz波形です。図6-2の波形と比較するとリンギングは一切なく大変きれいな信号が伝送できているようです。それではこの状態でスピードを上げた場合はどうでしょうか?

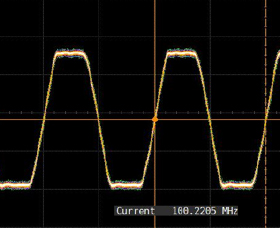

図8-2は同環境で周波数を100MHzに上げた波形です。33MHzと同様でリンギングの反射はなく、きれいな波形です。このエッジレートであれば100MHzでも振幅は減衰していないので、さらに周波数を上げて、信号の反射が発生するか確認します。

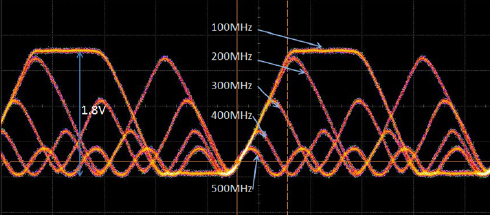

さらにクロックの周波数を上げた波形が図9です。図9では時間軸のスケールを広げ、先ほどの100MHzクロック波形の上に200MHz、300MHz、400MHz、500MHzを上書きしています。

終端抵抗の実装されたこの伝送路では、1.8V振幅で33MHzの約6倍の200MHzクロックまではリンギングもなく、振幅もほとんど低下していません。この200MHzクロックの環境は400Mbpsと同等になります。

この評価は実際の基板上の配線よりも非常に長い1mの同軸ケーブルを使用していますが、長い伝送路でも反射のない伝送が可能でした。

このように振幅の大きなシングルエンド信号でも伝送路の特性インピーダンスに合わせた抵抗を終端に置くことで、スピードに関係なく反射を抑えたきれいな信号伝送ができることが分かりました。

しかし、1.8V振幅で伝送路の特性インピーダンスが50Ωの場合は、終端器も50Ωを使用することとなり、終端部で消費される電流を計算すると1チャンネル(ch)当たりI=36mA(1.8V=I×50Ω)の大電流を流さなくてはならず、現実的ではありません。

もう1つの問題が振幅です。図9の300MHz,400MHz,500MHzと周波数を上げていくと、送信側ドライバのエッジレートの関係で徐々に振幅が小さくなり、振幅を保ったまま速くできませんでした。

500MHzでは1.8Vの4分の1以下の400mV程度まで振幅が低下しており、この状態では1.8VのシングルエンドCMOSレシーバーは正常にHigh・Lowの信号を受信できません。

この500MHzクロックは1Gbpsと同等で、400mVの振幅はLVDSの350mVとほぼ同じレベルの振幅となっています。

「1)差動信号は高速性に優れている」で前述したようにCMLドライバはエッジレートが高速ですが、小振幅のシングルエンドでも使用可能です。

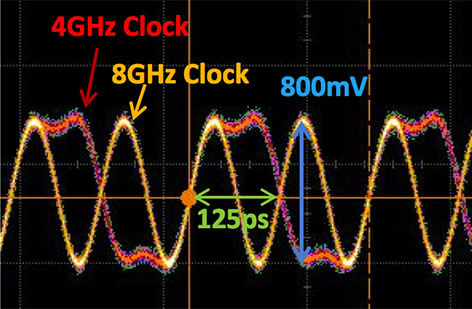

図10は振幅を800mVシングルエンドとしたCMLの高速エッジレートの2種類のクロック波形です。

CMLシングルエンドの4GHzと8GHzクロック波形の振幅は双方減衰せずトグルできています。8GHzのクロックは16Gbpsの通信速度と等価になります。

伝送路の終端に伝送路の特性インピーダンスに合わせた終端器を実装すると、差動やシングルエンド、振幅の大小に関係なく反射が抑えられるため、リンギングのないきれいな信号伝送が可能なことが分かりました。また0Hzから高速なエッジレートの場合は10Gbpsを超える通信でもスピードに関係なく反射のない伝送が可能になります。

シングルエンドの高速伝送でも小振幅であれば速いエッジレートを持つCMLを使用することで、技術的な問題はなさそうです。

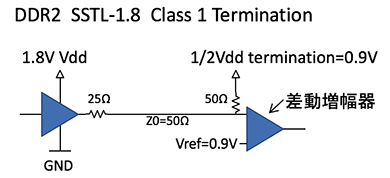

シングルエンドで高速伝送を行うアプリケーションとしては、DDR2やDDR3メモリで採用されている図11のSSTL(JEDEC Stub Series Terminated Logic)や放送、映画の画像伝送で使用されるSDI(SMPTE Serial Digital Interface)などがあります。

SSTLの受信側ではLVDSやCMLの差動と同様に差動増幅器を採用し、差動の片側だけを信号入力に使用しています。もう片方の差動入力にはリファレンス電圧(通常1/2Vdd)に接続し、入力信号はこのリファレンス電圧を境界としてトグルし、レシーバーは0、1信号を認識します。

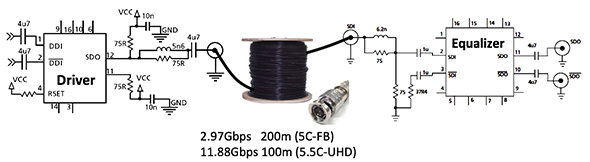

またSDIでは図12の構成で高エッジレートのドライバ、単位長あたりのロスが非常に少ない高周波同軸ケーブル、厳格なリターンロス仕様、シリアル電気通信で最高クラスのACゲインイコライザーなどの採用でシングルエンド800mV、2.97G〜11.88Gbpsの帯域でも100mを超える長距離伝送を実現しています。

Copyright © ITmedia, Inc. All Rights Reserved.