高速伝送の代表的な物理層 LVDS・PECL・CML:高速シリアル伝送技術講座(3)(2/4 ページ)

今回は、高速差動伝送で使用されている代表的な物理層である「LVDS」「PECL」「CML」の特長、接続方法、用途例を紹介していきます。

LVDS(ローボルテージ ディファレンシャル シグナリング)

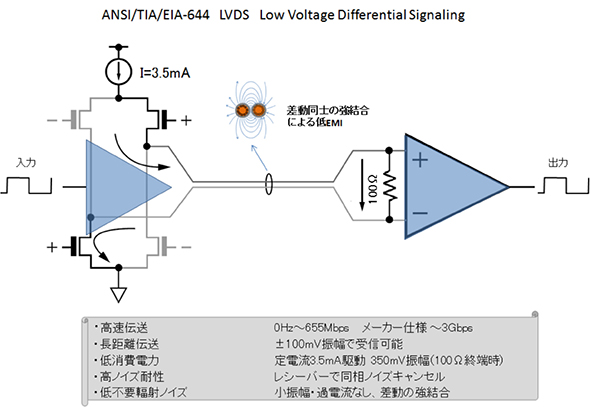

LVDS(Low Voltage Deferential Signaling)は1995年、ANSI/TIA/EIA-644 LVDSとして承認された物理層の仕様です。

このLVDSの仕様は他の規格からも参照できるように単純な0/1信号を伝送する物理層として定義され上位層の仕様は含まれず、また伝送媒体も規定されていません。

LVDSの代表的なスペックを図2に示します。

LVDSの最大伝送スピードは規格上655Mビット/秒(bps)、メーカー仕様として3Gbps程度までをサポートする製品も多数あります。仕様上3.5mAの定電流源駆動のため、低消費電力で振幅が小さく、不要輻射ノイズも限定的です。受信端では送信振幅±350mVの3分の1以下±100mVの振幅があれば受信でき、長距離や高速伝送が可能になります。ケーブルの長さやその特性については使用するメディアに依存するため規定せず、設計者により自由に選択が可能です。

通常DC接続で使用されるため、AC結合の際に必要なデータ遷移の制限がなく、0Hzから最大周波数までのバイナリ信号をそのまま伝送できます。もちろんCMLやPECL同様にコーディングを工夫することでAC結合も採用できます。

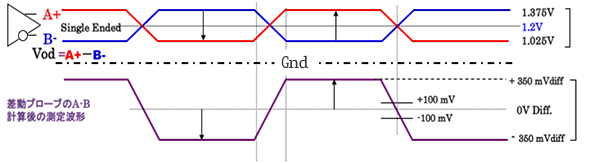

差動の2本A+、B−の各信号は図3(上側)のように1.2Vのコモンモード電圧(Vcm)を中心として、100Ω終端では3.5mAの定電流源駆動により、他方を基準にして矢印方向に350mVの電位差で振幅します。この2本の信号の振幅差(A+)−(B−)が差動振幅で、オシロスコープの差動プローブで測定される波形は図3(下側)になります。

オシロスコープの差動プローブでの測定では、図3(下側)のようにA−Bの計算後の結果を表示するため、−350mVから+350mVまでの計700mVの振幅が物理的に存在しているように表示されますが、計算上の波形で実際は存在していません。通常のシングルエンド波形の測定と分けるため、この波形は700mVpp differentialと表現しています。また差動プローブの測定はA-Bを計算するためにコモンモード電圧の情報がなくなっています。

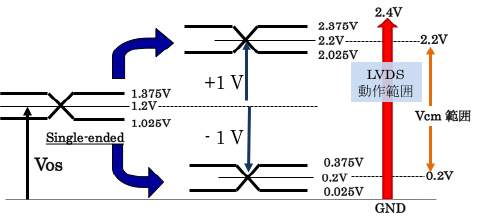

図4はLVDSレシーバーのコモンモード電圧範囲Vcmを示しています。送信側はコモンモード電圧1.2V(Typ)で出力しますが、ANSI/TIA/EIA-644Aの規定の通り、受信側はコモンモード電圧が0.2〜2.2Vであれば受信可能です。

| Vod | Driver Differential Output Voltage | ±250〜450mV |

|---|---|---|

| Vos | Driver Offset Voltage | ±1.25V |

| Vth | Receiver Thresholds | ±100mV |

| Vin | Receiver Input Voltage Range | GND to 2.4V |

| Vcm | Common-Mode Range | 1.25V±1V |

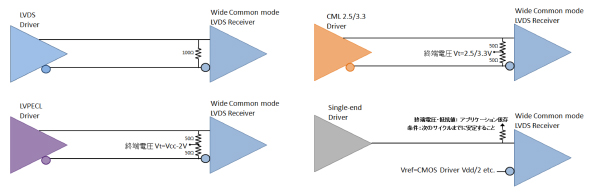

GNDからVdd電圧近辺までというさらに広い範囲のコモンモード電圧を受信可能なLVDS製品も多くリリースされています。それら製品では使用電源範囲内の差動信号をほぼ受信できます。そのため、帯域を満たせば図5のようにDC接続で他の差動信号仕様やシングルエンド信号でもワイドコモンモードレンジのLVDSレシーバーで受信でき、LVDS物理層製品の特長の1つといえるでしょう。

LVDSの使用用途はCMOS/TTLシングルエンド信号の高速化や距離の延長、低EMIなど多岐にわたります。アプリケーションの例としてはLCDパネルの画像I/F、マシンビジョンのケーブルI/F、イメージセンサー出力部、マルチファンクションプリンタ、通信インフラ、交換機の機器内バス信号I/Fなどが挙げられます。

Copyright © ITmedia, Inc. All Rights Reserved.