高速伝送の代表的な物理層 LVDS・PECL・CML:高速シリアル伝送技術講座(3)(3/4 ページ)

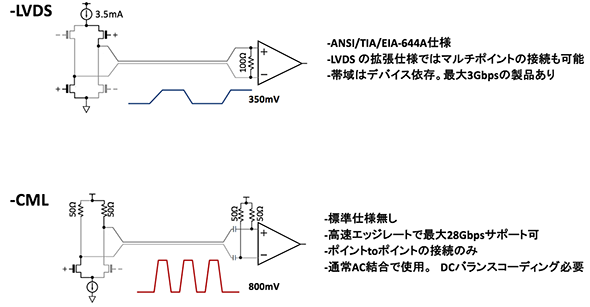

今回は、高速差動伝送で使用されている代表的な物理層である「LVDS」「PECL」「CML」の特長、接続方法、用途例を紹介していきます。

ECL(エミッターカップルドロジック)

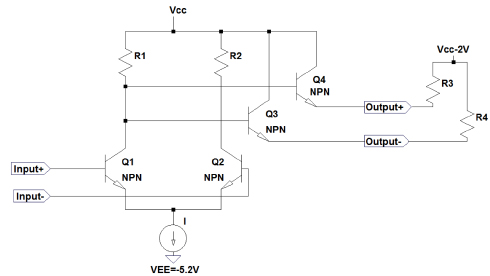

1971年にMotorolaからエミッターカップルドロジックECL10Kファミリー、1973年にFairchild Semiconductorから3倍程度高速な100Kファミリーが発表されました。当時、高速化が要求される大型コンピュータや通信機器、計測機器などで使用されていました。ECL出力段の等価回路を図6に示します。

ECLは名前の通りトランジスタQ1、Q2のエミッタが結合しており、定電流源Iを通してマイナス電源のVEEに接続されています。またコレクタ側Vccは通常0Vに接続されます。

この構成で分かるようにECLではマイナス電源が必要なことや汎用ロジックと非互換、消費電力の高さなどから一般的なアプリケーションに広がることはありませんでした。

その後、負電源を正電源に変えたPositive ECL(PECL)や低電圧版のLVPECLが開発され、大型コンピュータ、スーパーコンピュータなどのハイパフォーマンスコンピューティング(HPC)アプリケーションや通信インフラなどで引き続き採用されました。また現在各高速規格が採用しているCML(Current Mode Logic)の元となった技術でもあります。

特長は標準800mV振幅で高速なエッジレート、高消費電力、基本的に1対1(ピア・ツー・ピア)の接続になります。

PECLとLVPECLはLVDSと同様にプラス電源で動作できるようになりましたが、消費電力の大きさはECLと同等です。PECLやLVPECLの出力回路は図6のVEEをGND、Vccに正電源を供給する構成で基本的にECLと同じです。出力がポジティブ(Positive)/ネガティブ(Negative)の差動形式になっていますが、片方のみのシングルエンドとしても使用できます。

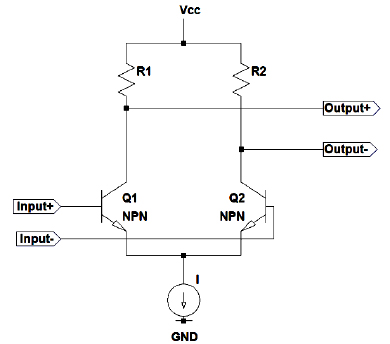

CML(カレントモードロジック)

CMLドライバは図6に示したECL等価回路のQ3、Q4のトランジスタを省いた等価回路のシンプルな構成(図7)です。消費電力は大きく、高速なエッジレートを作ることができます。LVDSの出力350mVと比較し、標準800mVの出力で1対1の接続構成です。高速性については一般的にLVDS<PECL<CMLの順番になります。

汎用の物理層なので、高速伝送が必要な部分で使用されていますが、PCIe、SATA、Display Port、V-by-One HS、SDI、USB 3.1、Thunderboltなどの高速規格もこのCML物理層を採用しています。

受信端ではLVDSは単純に100Ωなどの伝送路インピーダンスに合わせた終端器を置きますが、CMLではポジティブ/ネガティブピンを50Ωで電源に接続し終端しています。

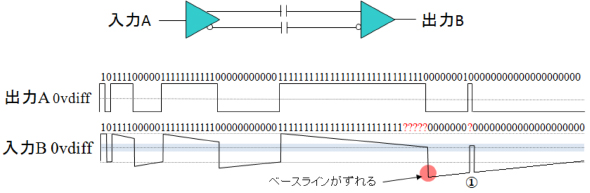

CMLの帯域は25Gbps以上に高速化できますが、LVDSのように規格化されておらず、製品や企業ごとに入出力の仕様が異なります。その違いを吸収するため、図8のCMLの接続図のようにコンデンサーを使用しAC結合で使用されます。

AC結合をするとDC成分が伝わらないために、0や1が長く連続するデータではAC結合のコンデンサーの放電により徐々に信号レベルが減衰し、正常に受信できないことはよく知られていますが、図9のベースラインがずれた状態から信号がトグルしても①の部分のように受信端で0、1判定のスレッシュホールドを超えない状態が起こり正常に受信できません。この現象をDCワンダー、DCインバランス、ベースラインワンダー、パソロジカル、この状態を発生させる特殊なデータパターンをキラーパターン、キラーパケット、パソロジカルパターンなどアプリケーションにより呼び方は異なりますが意味は同じです。

この問題を回避するため、AC結合のアプリケーションではランレングス(0や1の連続数)を短くする工夫と0と1の数を同数にするDCバランスのとれたコーディングを考慮する必要があります。

一部規格のデータコーディングでは特定条件下でDCバランスがうまく取れない現象があり、レシーバー側でヒステリシスフィードバックをかけて補償する方法や、送信側の上位層で0と1の数を合わせる処理を行うなどの対策を行ないます。

Copyright © ITmedia, Inc. All Rights Reserved.