接続形態(トポロジ)と特性インピーダンス:高速シリアル伝送技術講座(4)(1/5 ページ)

今回は接続形態(トポロジ)、特性インピーダンスについてです。LVDS系テクノロジーのさまざまなトポロジとその基本な構成、またPECLやCMLを使用して同機能を高速で実現する方法などについて紹介します。

LVDSの接続形態(トポロジ)

LVDSやM-LVDSの物理層では、ポイントtoポイント接続だけでなく、マルチドロップやマルチポイントといった接続形態(トポロジ)が使用でき、TTL/CMOSシングルエンド信号の同トポロジと比較すると、距離の延長やスピードの向上、バスの構成ではスロット数を増やすことが可能になります。

ここではLVDS系テクノロジーのさまざまなトポロジとその基本な構成、またPECLやCMLを使用して同機能を高速で実現する方法についても説明します。

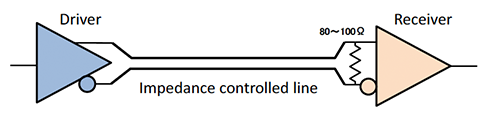

1)ポイント to ポイント

ポイント to ポイント接続は、LVDS、PECL、CMLで使用されている単純で高速性に優れた接続方法です。伝送路中の変化部位が少なくインピーダンスが管理された伝送路ほど信号品質は高くなり、高速伝送が可能となります。図1はLVDSのポイントtoポイント接続の例です。

受信端のアイパターン(EYE開口)は伝送路のインサーションロスやリターンロスの特性に依存します。

また伝送路の特性インピーダンスに合わせた終端抵抗を終端部に配置し反射を防ぎます。

PECLとCMLでは高速性が要求されるため、この接続方法に限定されています。

きれいな信号伝送にはコネクター、ケーブル、プリント配線板(PCB)、デバイスやその接続部を含んだ全体的なインピーダンスのコントロールが重要になります。

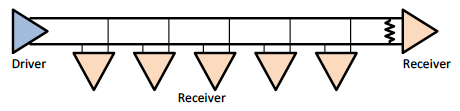

2)マルチドロップ

ドライバー1つにレシーバーが複数接続される、1対Nの構成です。終端のないシングルエンドのマルチドロップ構成をLVDSに変更してNの数を増やしたり、スピードの向上や伝送距離を延ばしたりが可能になります。

本来は枝分かれするレシーバーの終端部すべてにインピーダンス整合を行う終端器を実装すれば理想的ですが、ドライバーの負荷が大きくなり過ぎるため伝送路の最端のレシーバーにのみ終端を実装しています。

中間に接続される複数のレシーバーには終端抵抗はなく、レシーバー入力ピンはハイインピーダンスのため、配線のスタブ(枝分かれ)部分で反射が起こり、帯域が低下するため、可能な限りスタブ長を短くする必要があります。またレシーバー入力部の容量成分で高周波時に低いインピーダンスとなるため接続されるLVSDレシーバーの数は帯域やスタブの長さに依存し制限されます。M-LVDSの仕様では低速のエッジレートの採用により、最大32個までのマルチドロップ構成を行えるようになっています。

終端が図3のように2つあるマルチドロップの構成では双方の終端に終端器を実装します。この両終端の構成では振幅が半分になりノイズマージンが低下するため、M-LVDSなどの定電流源の大きなLVDS系ドライバーを使用します。

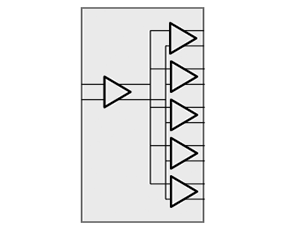

PECLやCMLではエッジレートが高速であるためにLVDSのようにマルチドロップのトポロジは採用しません。同機能を現実するために図4のような1対Nのデバイスを使用し高速信号を分配します。

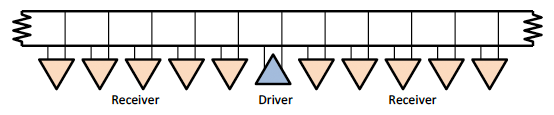

3)マルチポイント

マルチポイントは複数のドライバー、レシーバーを接続させたバス構成で、1つのドライバーのみがある時間に有効になり、他ノードの各ドライバーはハイインピーダンス(Hi-z)状態、各レシーバーは受信状態になります。

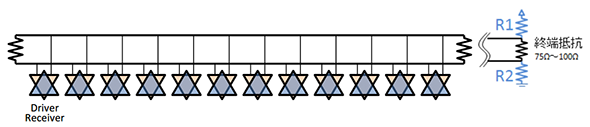

このバスの構成では2カ所を終端する両終端になり、負荷が増えるため、定電流源の大きなM-LVDS系のドライバーを使用します。どのドライバーもバスをドライブしない時間があるとバスがハイインピーダンス状態になりLVDSレシーバーがノイズを拾うため、ハイインピーダンス時に差動信号間に数十ミリボルト程度の小さい電位差を与える図5右側のように双方の終端抵抗部に外付けのフェイルセーフバイアス回路R1、R2を追加するか、M-LVDS Type2と呼ばれるレシーバーの信号スレッシュホールドを0Vdiffからオフセットを持たせた製品を使用し対応します。

ポイント to ポイントの接続でも、ドライバーがHi-zになる場合は、受信側が不確定になるのでこの外付けのフェイルセーフバイアス回路で同じように対応が可能になります。

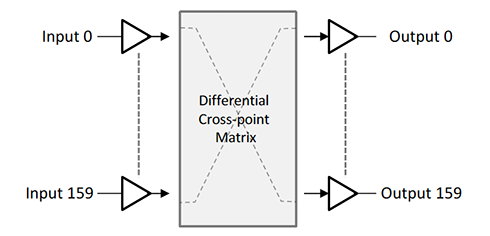

エッジレートの速いPECL、CMLではN対Nのクロスポイントスイッチ製品(図6)を使用し、入力信号を任意の出力にスイッチして接続することで帯域を犠牲にすることなく同様の機能をサポート可能です。

クロスポイントスイッチでは入力と出力の組み合わせが論理的にすべて可能なため、例えばInputXをOutputY(X・Yはポート番号)にそれぞれ出力する構成や、1つの入力を1対Nの複数の出力にアサインすることも可能です。またクロスポイントスイッチ製品の多くは各ポートとの遅延時間差が小さいため、レーン間のスキューをある程度許容するマルチレーンのアプリケーション(HDMI、DisplayPortなど)では、クロスポイントスイッチを使用しマルチレーンごとのスイッチも可能です。

Copyright © ITmedia, Inc. All Rights Reserved.