過電圧と低電圧の監視を低コストで実現する:Design Ideas パワー関連と電源(2/2 ページ)

マイクロプロセッサの電源管理には、一定の条件でマイクロプロセッサをリセットする信号を出力する機能を備えたスーパーバイザーICが広く使われている。安価なスーパーバイザーICは、電源電圧が設定値(下限値)を割り込んだときのみリセット信号を出力するものが多い。そこで、安価なシャント・レギュレーターICをスーパーバイザーICと組み合わせ、過電圧と低電圧の両方を監視できる回路を紹介する。

動作確認

実際にこの回路を試作して動作確認を行った。スーパーバイザーICはしきい値電圧が4.63Vの品種を用いている。従って電源電圧の下限値(VLOW)は4.63Vになる。R1とR2は10kΩのポテンショメーター(可変抵抗器)1個で代用した。R1が7.75kΩ、R2が2.25kΩになるようにポテンショメーターを設定した。すなわち電源電圧の上限値(VHIGH)を5.5Vに設定したことになる。

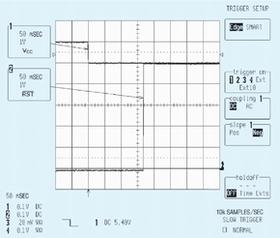

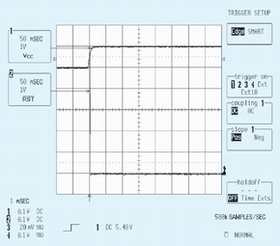

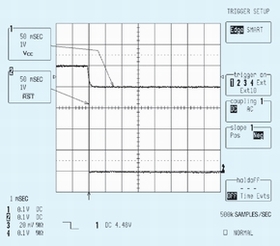

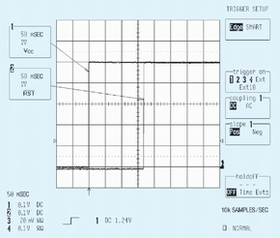

電源電圧が下限値よりも低いときは、リセット信号出力(RST)端子の論理レベルはローレベルのままである。この状態から電源電圧が上昇して下限値を超えると、RST端子は最短で140msの期間、ローレベルを維持した後、ハイレベルに遷移する(図2)。電源電圧が過電圧状態から下降して上限値に達し、正常値に戻った場合にも、RST端子は最短で140msの期間、ローレベルを維持してから、ハイレベルに変化する(図3)。また、電源電圧が正常値から上昇して上限値を超えると、RST端子が直ちにハイレベルからローレベルに変化してマイクロプロセッサをリセット状態に設定する(図4)。電源電圧が正常値から下降して下限値を割り込んだ場合にも、RST端子はすぐにハイレベルからローレベルに変化して、ローレベルを維持する(図5)。

図2:電源電圧が立ち上がるとリセット状態を解除 (クリックで拡大)

電源電圧が立ち上がるとリセット信号出力端子がハイレベルに遷移して、マイクロプロセッサのリセット状態を解除する。電源電圧が正常値に達してからリセット状態を解除するまでに最小140msの遅延時間を設けてある。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルター回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバー】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事から200本を厳選し、5つのカテゴリーに分けて収録した。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

整流回路の突入電流を簡単な部品で制限

整流回路の突入電流を簡単な部品で制限

簡単な部品で構成した突入電流制限回路を紹介する。 FPGAに向けた電源シーケンス回路

FPGAに向けた電源シーケンス回路

システムを設計する場合、電源投入と電源切断のときに発生する、コア電圧(内部回路に供給する電源電圧)とI/O電圧(入出力回路に供給する電源電圧)のタイミングと、その電圧差に注意を払う必要がある。電源投入/切断時に3.3Vの入力電圧を1.8Vのコア電圧に変換し、I/O電圧は3.3Vを保つようにして、2つの電源電圧の差を最小に抑える回路を紹介する。 リニア・レギュレーターを低コストDC-DCコンに

リニア・レギュレーターを低コストDC-DCコンに

高効率の電源を必要とするものの、高価なDC-DCコンバータICを使いたくない技術者に向けて、リニア・レギュレーターを使った安価なDC-DCコンバータを紹介する。 突入電流を低減できる時間遅延リレー

突入電流を低減できる時間遅延リレー

今回は、機械式接点を用いるスイッチを使う際の突入電流を抑える方法を紹介する。スイッチング動作時だけ直列抵抗を挿入するものだ。 昇圧型レギュレーターに降圧動作を追加する

昇圧型レギュレーターに降圧動作を追加する

SEPICレギュレータには、変換効率や磁性部品の点で欠点がある。そこで、SEPICレギュレータの代わりとして使える回路を提案する。 電池で駆動可能なツェナー電圧計測回路

電池で駆動可能なツェナー電圧計測回路

ツェナーダイオードのツェナー電圧(降伏電圧)を計測するには、そのツェナー電圧よりも高いDC電圧が必要である。加えて、負荷に流れる電流についても考慮しなくてはならない。