実装面積を削減するオペアンプとコンパレーター:日本TI TLV9061、TLV7011

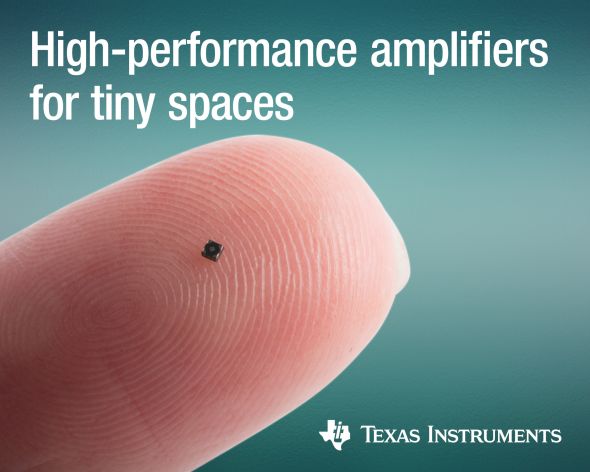

日本テキサス・インスツルメンツは、0.8×0.8×0.4mmの5ピンX2SONパッケージで供給する小型オペアンプ「TLV9061」と低消費電力のコンパレーター「TLV7011」ファミリーを発表した。

基板実装面積0.64mm2でシステムサイズを低減

日本テキサス・インスツルメンツは2018年2月、0.8×0.8×0.4mmの5ピンX2SONパッケージにより、基板実装面積を0.64mm2に抑えたオペアンプ「TLV9061」と低消費電力のコンパレーター「TLV7011」ファミリーを発表した。1000個購入時の単価は、TLV9061が0.19米ドルから、TLV7011が0.25米ドルからとなる。

TLV9061は、EMIフィルター付き入力を内蔵し、ディスクリート構成の外付け部品を大幅に削減できる。広帯域、高性能システム向けに開発され、10MHzのゲイン帯域幅、6.5V/μsの高スルーレート、10nV/√Hzの低ノイズ密度を提供する。動作温度範囲は−40〜125℃で、オフセットドリフトと入力バイアス電流の代表値を半減し、高いDC精度を可能にした。

TLV7011は、位相反転がない他、過大入力に対するヒステリシス特性を内蔵した。高い柔軟性を備え、外付け部品を削減できる。電源電圧は1.6〜5.5Vで、伝送遅延時間は最小260ナノ秒。より高速の応答性を備えながら、消費電力を最小335nAに抑えた。

両製品とも、レールツーレール入力と最小1.8Vの低電圧動作をサポート。各種の電池動作アプリケーションで活用できる。

同社では、携帯電話やウェアラブル、光モジュール、モータードライブ、スマートグリッド、電池動作のシステムなど、IoT(モノのインターネット)やパーソナルエレクトロニクス製品、産業用アプリケーションでシステムサイズを低減できるとしている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

静止電流650nAのナノパワーゼロドリフトオペアンプ

静止電流650nAのナノパワーゼロドリフトオペアンプ

日本テキサス・インスツルメンツは、静止電流650nAのナノパワーゼロドリフトオペアンプ「LPV821」を発表した。独自の自動較正技術を採用し、最大20μVの低いオフセット電圧を可能にした。 動作電流を5μAに低減したアナログコンパレーター

動作電流を5μAに低減したアナログコンパレーター

STマイクロエレクトロニクスは2016年11月、デュアル/クアッド型の16V CMOSアナログコンパレーターを発表した。コンパレーター当たりの標準動作電流を5μAに低減しているという。 外付け部品が少ない低コストのピーク検出器

外付け部品が少ない低コストのピーク検出器

今回は、整流ダイオードが不要で、Texas Instrumentsの高速コンパレーター「TLC372」のオープンドレイン出力を活用した、外付け部品が少ない低コストの正側ピーク電圧検出器を紹介する。 負性抵抗でオペアンプの負荷を打ち消す

負性抵抗でオペアンプの負荷を打ち消す

高精度のオペアンプは、高い開ループ利得、低いオフセット電圧/電流、低い電圧/電流雑音、低いひずみを実現している。しかし、すべての仕様を高い精度に維持したままで、高い出力電流を供給するのは難しい。これを解決する方法の1つは、負荷を打ち消すことだ。 オペアンプのダイナミック応答の検討(1) タイプ2補償回路の使用時

オペアンプのダイナミック応答の検討(1) タイプ2補償回路の使用時

補償回路は、理想的な特性を想定したオペアンプを中心に構築したアクティブ回路が使用されます。ですが、理想的なオペアンプを想定した計算は成立せず、最終的にゲインと位相の深刻な歪みを招く結果になります。開ループゲインと、低周波および高周波にある2つの極が全体的な応答の形状をどのように規定するかが明らかになると、適切なオペアンプを選択できます。 オペアンプのダイナミック応答の検討(2) タイプ2補償回路の伝達関数

オペアンプのダイナミック応答の検討(2) タイプ2補償回路の伝達関数

第2部では、2つの極の概要とそれらがフィルターの最終的な性能に対してもたらす歪みについて考察しながら、タイプ2の補償回路の伝達関数を決定する方法を説明します。