高速インタフェースで使用されるSerDes 〜 種類と特長、その歴史:高速シリアル伝送技術講座(9)(1/5 ページ)

代表的な3種類のシリアライザ(Serializer)とデシリアライザ(De-serializer)の機能と歴史について説明していきます。

SerDesの種類と特長、歴史について

前回と前々回は高速信号伝送のための伝送路について説明しました。これらの伝送路はシリアライザ(Serializer)とデシリアライザ(De-serializer)を使用した高速シリアル伝送で使用されていますが、「なぜ高速シリアル伝送を使用するのか」という理由と、代表的なシリアライザ(Serializer)/デシリアライザ(De-serializer)の種類や特長、その歴史について説明していきます。

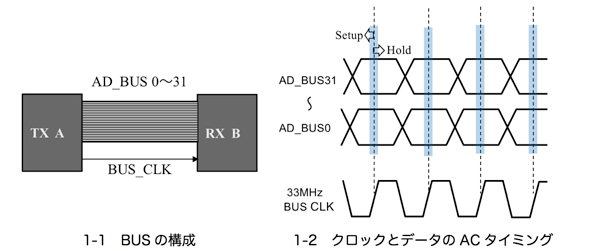

コンピュータシステム内部のデータ伝送の一例として、図1-1のようにデバイスAからデバイスBへ、32ビットバスのデータを転送しています。図1-1ではデバイスAとBの距離が短く、バスクロックのスピードは33MHzと高速でないため、図1-2の受信側クロックの立ち上がりエッジでバスデータをサンプルする際に必要な、水色で示されたデータの安定領域(セットアップ・ホールド)は問題なく、正常なデータ伝送が可能な状態です。

TX側デバイスAのデータ処理能力が4倍に向上すると、バスから出力されるデータ量は4倍になるため、以下の2つの方法で、デバイスAとデバイスBのバス部分の接続方法を検討していきます(電子機器内部のバス仕様は一般に公開されませんが、PC内部バスの仕様は公開されているため、PCのアプリケーションを例に、以下に説明していきます)

1. バス幅を4倍にする。

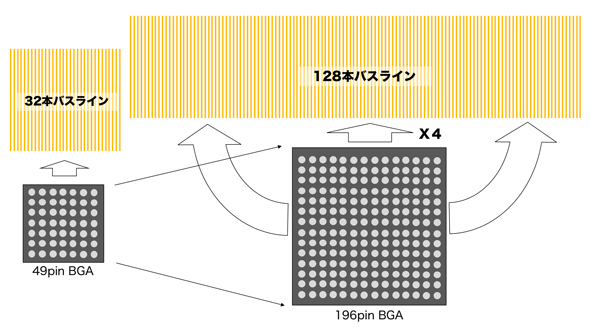

1つ目はバス幅を32ビットの4倍の128ビットにする方法です。

図2の左側デバイスはBGAパッケージを使用し、電源ピン(IOVcc、IOGND)も含めた32ビットI/Oで必要なピンを配置した場合の一例です(条件:I/O 4ピンにつき1組のVcc、GNDを配置=48ピン<49ピンBGA)。この程度のピン数であれば、四辺にピンを配置した安価なQFPやQFNパッケージも使用可能です。

図2の右側の大きなBGAパッケージは同条件で128ビットI/Oを配置した例です。

32ビットの4倍の128ビットのバスをサポートすると、図2右側のピン数(もしくはそれ以上)のパッケージになります。またデバイスのI/Oや電源ピンの増加と同様にPCB上の配線も大幅に増え、この配線をPCBの表層のみのマイクロストリップラインで配線した場合、配線面積が大きく、クロックとデータのACタイミングを合わせるため、配線長を等長とするミアンダ配線を行うとさらに配線領域が広がります。PCBの層数を増やしバス配線を内層とすると解決できますが、基板コストが上昇します。

8ビットバスから4倍の32ビット程度のバス幅の拡張は可能でしたが、32ビットを4倍の128ビットにするとデバイスのピン数の増大とI/O増加に伴う消費電力の上昇、また基板上の配線も4倍に増え、コネクターを介する場合は、コネクターのピン数も大幅に増えることになります。また同長配線の困難や基板の層数の増加でコストが大幅に上昇するため、この方法は現実的な選択肢ではありませんでした。

Copyright © ITmedia, Inc. All Rights Reserved.