چ‚‘¬ƒCƒ“ƒ^ƒtƒFپ[ƒX‚إژg—p‚³‚ê‚éSerDes پ` ژي—ق‚ئ“ء’·پA‚»‚ج—ًژjپFچ‚‘¬ƒVƒٹƒAƒ‹“`‘—‹Zڈpچuچہپi9پjپi2/5 ƒyپ[ƒWپj

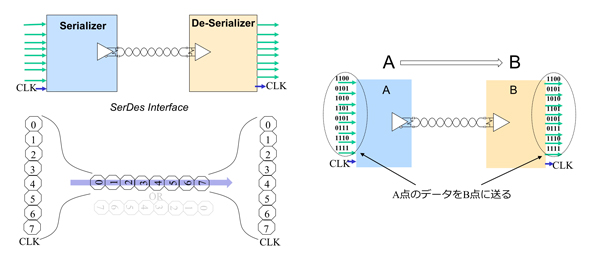

‘م•\“I‚ب3ژي—ق‚جƒVƒٹƒAƒ‰ƒCƒUپiSerializerپj‚ئƒfƒVƒٹƒAƒ‰ƒCƒUپiDe-serializerپj‚ج‹@”\‚ئ—ًژj‚ة‚آ‚¢‚ؤگà–¾‚µ‚ؤ‚¢‚«‚ـ‚·پB

2. ƒNƒچƒbƒNƒXƒsپ[ƒh‚ً4”{‚ة‚·‚é

پ@’ل‘¬‚جƒoƒXƒNƒچƒbƒN8MHz‚ًƒoƒXƒfپ[ƒ^‚ئ‚جACƒ^ƒCƒ~ƒ“ƒO‚ً–‚½‚µ4”{‚ج33MHz‚ض‚جŒüڈم‚ح‰آ”\‚إ‚µ‚½پBژہچغپAPC-AT‚جISAƒoƒX‚حƒNƒچƒbƒNƒXƒsپ[ƒh8.33MHzپA‚»‚جŒم”•\‚³‚ꂽPCIƒچپ[ƒJƒ‹ƒoƒX‚إ‚ح33MHz‚ًچج—p‚µپAƒNƒچƒbƒN‚ح4”{‚جƒXƒsپ[ƒh‚ئ‚ب‚è‚ـ‚µ‚½پB

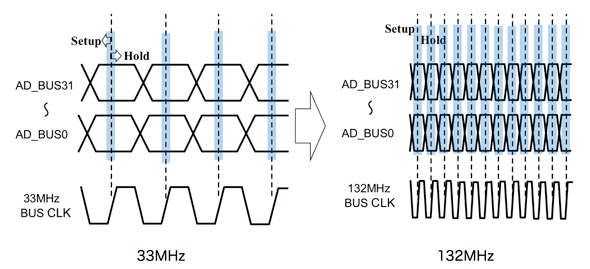

پ@‚µ‚©‚µ‚±‚ج33MHz‚جƒNƒچƒbƒNƒXƒsپ[ƒh‚ً4”{‚ج132MHz‚ئ‚·‚é‚ئپAژَگM‘¤‚إ‚جƒoƒXگMچ†‚جƒfپ[ƒ^‚ئƒNƒچƒbƒN‚جACƒ^ƒCƒ~ƒ“ƒO—vŒڈپiƒZƒbƒgƒAƒbƒvپEƒzپ[ƒ‹ƒhپj‚ً–‚½‚·‚±‚ئ‚ھچ¢“ï‚ة‚ب‚è‚ـ‚µ‚½پiگ}3پj

پ@‚ـ‚½ƒNƒچƒbƒNƒXƒsپ[ƒh‚ًڈم‚°‚邱‚ئ‚إپAƒoƒXƒVƒXƒeƒ€–{—ˆ‚ج•،گ”ƒXƒچƒbƒg‚جƒTƒ|پ[ƒg‚ھگMچ†•iژ؟پiSignal Integrityپjˆ«‰»‚ج‚½‚ك‚ة‘ه•‚ةŒ¸ڈ‚µ‚ـ‚µ‚½پB1992”N‚ة”•\‚³‚ꂽ33MHz‚جPCI Local Bus Rev 1.0‚إ‚ح4–{‚جƒoƒXƒXƒچƒbƒg‚ًƒTƒ|پ[ƒg‚µ‚ؤ‚¢‚ـ‚µ‚½‚ھپAƒNƒچƒbƒN‚ًچ‚‘¬‰»‚µ‚½PCI-X Rev1.0‹Kٹiپi1999”Nپj‚إ‚حƒNƒچƒbƒNƒXƒsپ[ƒh‚جڈمڈ¸‚ة”؛‚¢100MHzƒNƒچƒbƒN‚إ‚ح2–{پA133MHz‚إ‚ح1–{‚جƒXƒچƒbƒg‚ئ‚ب‚èپAƒXƒچƒbƒgگ”‚ھ‘ه‚«‚Œ¸ڈ‚µ‚ـ‚µ‚½پB

پ@1980”N‘مŒم”¼‚©‚ç1990”N‘م‚ة‚©‚¯‚ؤپAƒpƒ‰ƒŒƒ‹‚جƒoƒXگMچ†چ\گ¬‚ج‚ـ‚ـپAƒoƒX•‚جٹg’£‚ئƒpƒ‰ƒŒƒ‹ƒNƒچƒbƒNژü”gگ”‚ًڈم‚°‚éژè–@‚إ8MHzپ^16ƒrƒbƒg‚جISAƒoƒX‚©‚ç32ƒrƒbƒgƒoƒXژd—l‚جEISAƒoƒX‚âپA32/64ƒrƒbƒgƒoƒXپE33پ^66MHzƒNƒچƒbƒN‚جPCIپA100پ^133MHzƒNƒچƒbƒNژd—l‚ً’ا‰ء‚µ‚½PCI-X‚ب‚ا‚ھچô’肳‚ê‚ـ‚µ‚½پB‚µ‚©‚µ‚ب‚ھ‚çپAƒfƒoƒCƒX‚جژwگ”“I‚بڈˆ—”\—ح‚جڈمڈ¸‚ة’ا‚¢‚آ‚‚±‚ئ‚ح‚إ‚«‚ـ‚¹‚ٌ‚إ‚µ‚½پB

پ@‚ـ‚½ƒfƒoƒCƒXA‚ئƒfƒoƒCƒXB‚ج‹——£‚ھ—£‚ê‚ؤ‚¢‚éڈêچ‡‚àپAƒoƒXƒfپ[ƒ^‚ئƒNƒچƒbƒN‚جACƒ^ƒCƒ~ƒ“ƒO—vŒڈ‚ھ”j‚½‚ٌ‚·‚邽‚كپAƒfپ[ƒ^‚جگ³ڈي‚بژَگM‚ھ•s‰آ”\‚ة‚ب‚è‚ـ‚·پB

پ@‚±‚جƒpƒ‰ƒŒƒ‹ƒoƒX‚ج–â‘è‚ً‰ًŒˆ‚·‚éژè–@‚ئ‚µ‚ؤپASerDes‚جƒAپ[ƒLƒeƒNƒ`ƒƒ‚ھچج—p‚³‚ê‚ـ‚µ‚½پBƒVƒٹƒAƒ‰ƒCƒUپiSerializerپj‚ئƒfƒVƒٹƒAƒ‰ƒCƒUپiDe-serializerپj‚ً‚ـ‚ئ‚ك‚ؤپASerDesپiƒTپ[ƒfƒXپj‚ئŒؤ‚ٌ‚إ‚¢‚ـ‚·پB‚±‚ج‹@”\‚حگ}4چ¶‚ج‚و‚¤‚ةƒVƒٹƒAƒ‰ƒCƒU‚إƒpƒ‰ƒŒƒ‹‚جƒoƒXگMچ†‚ًƒVƒٹƒAƒ‹‰»‚µپAƒfƒVƒٹƒAƒ‰ƒCƒU‚إ‚±‚جƒVƒٹƒAƒ‹گMچ†‚جƒfپ[ƒ^‚ًŒ³‚جƒpƒ‰ƒŒƒ‹ƒoƒX‚جگMچ†‚ة–ك‚·’Pڈƒ‚بژd—l‚إ‚·پBƒVƒٹƒAƒ‰ƒCƒUA‚ة“ü—ح‚µ‚½ƒoƒXƒfپ[ƒ^‚ئ“¯ٹْƒNƒچƒbƒN‚حگ}4‰E‚ج‚و‚¤‚ةƒfƒVƒٹƒAƒ‰ƒCƒUB‚©‚瓯—l‚ةڈo—ح‚³‚ê‚ـ‚·پB

پ@ƒpƒ‰ƒŒƒ‹ƒoƒXچ\‘¢‚إ‚ح“`‘—‹——£‚ج‰„’·‚âپAƒNƒچƒbƒNژü”gگ”‚ًڈم‚°‚邱‚ئ‚ھچ¢“ï‚ب‚½‚كپA‹——£‚ج‚ ‚é“`‘—‚âچ‚‘¬“`‘—‚إ‚حپASerDes‚جƒVƒٹƒAƒ‹‰»‚ج‹@”\‚ًژg—p‚µپAƒfƒoƒCƒXA‚©‚çƒfƒoƒCƒXB‚ضƒfپ[ƒ^‚ً“`‘—‚µ‚ؤ‚¢‚ـ‚·پB

Copyright © ITmedia, Inc. All Rights Reserved.