چ‚‘¬ƒCƒ“ƒ^ƒtƒFپ[ƒX‚إژg—p‚³‚ê‚éSerDes پ` ژي—ق‚ئ“ء’·پA‚»‚ج—ًژjپFچ‚‘¬ƒVƒٹƒAƒ‹“`‘—‹Zڈpچuچہپi9پjپi4/5 ƒyپ[ƒWپj

‘م•\“I‚ب3ژي—ق‚جƒVƒٹƒAƒ‰ƒCƒUپiSerializerپj‚ئƒfƒVƒٹƒAƒ‰ƒCƒUپiDe-serializerپj‚ج‹@”\‚ئ—ًژj‚ة‚آ‚¢‚ؤگà–¾‚µ‚ؤ‚¢‚«‚ـ‚·پB

پy2پz01ƒNƒچƒbƒN–„‚كچ‚فژ®SerDes

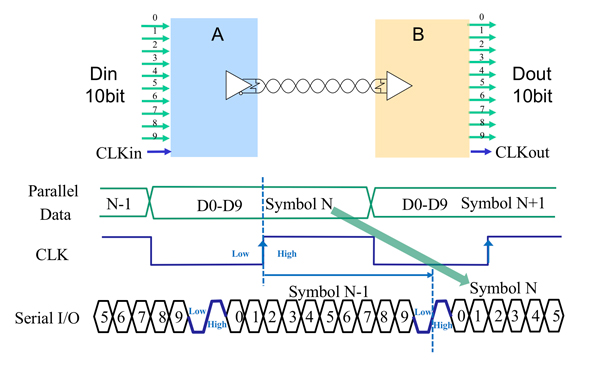

پ@LVDS SerDes‚ھ”•\‚³‚ꂽ3”NŒم‚ج1998”NپAگ}9‚جƒpƒ‰ƒŒƒ‹ƒoƒX‚جƒNƒچƒbƒNLowپi0پj‚ئHighپi1پj‚ًƒXƒ^پ[ƒg‚ئƒXƒgƒbƒvƒrƒbƒg‚ئ‚µ‚ؤƒVƒٹƒAƒ‹ƒfپ[ƒ^‚ة–„‚كچ‚ٌ‚¾پA01

پiƒ[ƒچƒCƒ`پjƒNƒچƒbƒN–„‚كچ‚فژ®SerDes‚ھ”•\‚³‚ê‚ـ‚µ‚½پBƒXƒ^پ[ƒgƒXƒgƒbƒvƒNƒچƒbƒN–„‚كچ‚فژ®‚ئ‚àŒؤ‚خ‚ê‚ؤ‚¢‚ـ‚·پB

پ@‚±‚جƒfƒoƒCƒX‚حLVDS SerDes‚جƒAپ[ƒLƒeƒNƒ`ƒƒ‚ج—¬—p‚إگفŒv‚³‚êپAچ‚‘¬‰»‚â’·‹——£‰»‚جچغ‚ة‰غ‘è‚إ‚ ‚ء‚½LVDS SerDes‚جƒNƒچƒbƒN‚ئƒfپ[ƒ^‚جƒXƒLƒ…پ[‚ج–â‘è‚ً‰ًŒˆ‚µ‚ـ‚µ‚½پB

پ@چإڈ‰‚جگ»•i‚حگ}9‚ج10ƒrƒbƒg‚جƒVƒٹƒAƒ‹ƒfپ[ƒ^‚ة0پA1‚جƒNƒچƒbƒNڈî•ٌ‚ً–„‚كچ‚ٌ‚¾Œv12ƒrƒbƒg‚جƒVƒٹƒAƒ‹•دٹ·‚إ‚µ‚½‚ھپA‚»‚جŒمƒfپ[ƒ^ƒrƒbƒg‚ً‘‚₵پA18پA20پA21پA26پA31پA66پA67پA130پA132‚ب‚ا‚جƒVƒٹƒAƒ‹ƒrƒbƒgگ»•i‚â‹Kٹi‚ھ””„پA”•\‚³‚ê‚ؤ‚¢‚ـ‚·پB

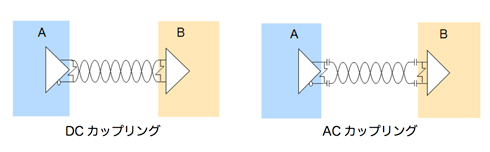

پ@ƒVƒٹƒAƒ‰ƒCƒUپiTXپj‚ئƒfƒVƒٹƒAƒ‰ƒCƒUپiRXپj‚ج‹——£‚ھ—£‚ê‚é‚ئŒآ•ت‚ج“dŒ¹‚ًژg—p‚·‚邽‚ك‚ةپA“dŒ¹“dˆتچ·پiGND“dˆتپj‚ض‚ج”z—¶‚ھ•K—v‚ة‚ب‚è‚ـ‚·پB‚±‚ج“dˆتچ·‚ج–â‘è‚ً‰ًŒˆ‚·‚邽‚كپAƒfپ[ƒ^ƒ‰ƒCƒ“‚ةACƒJƒbƒvƒٹƒ“ƒOپiگ}10‰Eپj‚ًژg—p‚µ‚ؤ‚¢‚ـ‚·پB‚ـ‚½TX‚ئRX‚جGND“dˆت‚ھ“¯‚¶‚إ‚àپACML I/O‚إ‚ح‘—گM‚ئژَگM‘¤‚ج•¨—‘w‚ھ‚»‚ꂼ‚êچإ“K‚بƒRƒ‚ƒ“ƒ‚پ[ƒh“dˆ³‚إ“®چى‚إ‚«‚é‚و‚¤پA“¯—l‚ةACƒJƒbƒvƒٹƒ“ƒO‚ھˆê”ت“I‚ةژg—p‚³‚ê‚ؤ‚¢‚ـ‚·پB

پ@ACƒJƒbƒvƒٹƒ“ƒO‚ًچs‚¤‚ئDC‚ئ’لژü”gگ¬•ھ‚ھ“`‘—‚إ‚«‚ب‚¢‚½‚كپAACƒJƒbƒvƒٹƒ“ƒO‚إSerDes‚ً“®چى‚³‚¹‚éڈêچ‡‚حپAƒfپ[ƒ^ƒXƒgƒٹپ[ƒ€‚جDCƒoƒ‰ƒ“ƒX‚ً•غ‚آ‚½‚ك‚جƒXƒNƒ‰ƒ“ƒuƒ‹‰»‚âDCƒoƒ‰ƒ“ƒXƒrƒbƒg‚ج’ا‰ءپAƒVƒٹƒAƒ‰ƒCƒU‘¤‚إDCƒoƒ‰ƒ“ƒX‚ً•غژ‚³‚¹‚邽‚ك‚ج“ءژêƒpƒ^پ[ƒ“‚جƒpƒfƒBƒ“ƒO‚ب‚اپA‹Kٹi‚âگ»•i‚ة‚و‚肳‚ـ‚´‚ـ‚ب‘خ‰‚ًچs‚ء‚ؤ‚¢‚ـ‚·پB

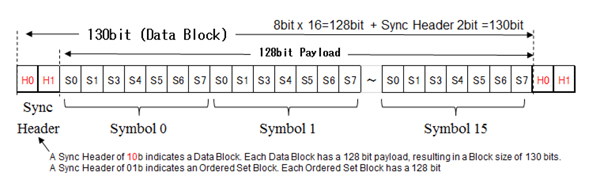

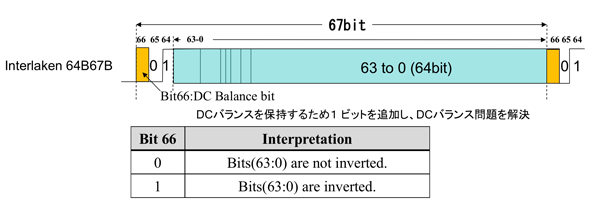

پ@10Gbps‚جƒCپ[ƒTپ[ƒlƒbƒg‹KٹiIEEE802.3ae 10GBase-R 10GBase-W‚إژg—p‚³‚ê‚ؤ‚¢‚é64B66Bپiگ}11-1پjپA‚»‚جƒfپ[ƒ^’·‚ً2”{‚ة‚µ‚½PCIe Gen3(8Gbps)‚ج128B/130Bپiگ}11-2پjپA64B66BƒRپ[ƒfƒBƒ“ƒO‚جDCƒoƒ‰ƒ“ƒX‚جژم“_‚ً‰ًŒˆ‚µ‚½Interlaken 64B67B’چ1(گ}11-3)پAPCIe Gen3‚إچج—p‚µ‚½128B130B‚جگM—ٹگ«Œüڈم‚ً–عژw‚µ‚½USB3.1 Gen2 SS+پi10.3Gbpsپj‚ج128B132B‚àپA‚±‚جƒXƒ^پ[ƒgƒXƒgƒbƒvƒNƒچƒbƒN–„‚كچ‚ف•ûژ®‚ة•ھ—ق‚³‚ê‚ـ‚·پB

گ}11-3پFInterlaken 64B67Bپ@ƒRپ[ƒfƒBƒ“ƒOپiƒfپ[ƒ^ƒڈپ[ƒh‘—گMژپj

’چ1پFhttp://www.interlakenalliance.com/Interlaken_Protocol_Definition_v1.2.pdfژQڈئ

Copyright © ITmedia, Inc. All Rights Reserved.