高速インタフェースで使用されるSerDes 〜 種類と特長、その歴史:高速シリアル伝送技術講座(9)(5/5 ページ)

代表的な3種類のシリアライザ(Serializer)とデシリアライザ(De-serializer)の機能と歴史について説明していきます。

【3】8B10B SerDes

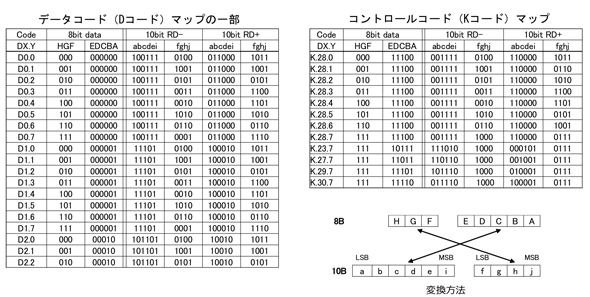

1983年にIBMのAl Widmer氏とPeter Franaszek氏により8B10Bのシリアルコーディング方式が発表されました。8ビットの信号をKコードと呼ばれるコントロールコードの追加とDCバランスを取るために1つのデータに対して2種類のコード(RD+/−)を割り当て、計10ビットに変換する仕様です(図12)

特長としてはランレングス(1や0の同一符号の連続数)を最大5として低周波帯域を制限していることと、データ中の1と0の数の差が常に+/−1以内となるようにDCバランスを取っており、シグナルインティグリティを向上させています。データ中の1と0の数の差が必ず+/−1以内が条件のため、この差を逸脱するとコーディングだけでデータエラーが判定できるようにもなっています。

この8B10Bコーディングは、古くからハイパフォーマンスコンピューティング(HPC)や通信インフラのアプリケーションで、光信号や電気信号の高速化や通信距離の延長に使用されている信頼性の高いコーディング方式です。

データの依存性がなくコーディング方式だけでDCバランスが取れるため、ACカップリングを使用する際は最適な選択肢になります。

この8B10Bコーディングでは帯域の制限(最低周波数=最大周波数×20%)がかかり、高帯域成分の減衰の大きなギガbps級の高速伝送や長い伝送路では、20%以下の低周波が存在しないために、ISIジッタを低減する効果があります。

01(スタートストップ)クロック埋め込み型コーディングの優位性の説明で、「8B10Bコーディングは8ビットを10ビット変換するために20%ロスになり変換効率が悪い」とだけ説明され、8B10Bの本来の優位性の説明がない場合が残念ながら多く見受けられます。

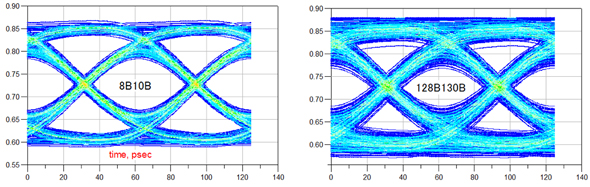

それではロスのある伝送路を通過した場合、このコーディング方式の違いでどの程度入力端でのISIジッタに差があるのか、8B10Bと128B130Bを比較してみましょう。

どのようなデータを入力した場合でも8B10Bコーディングでは図13左のEYEの開口率は変わりませんが、図13右の128B130Bコーディングのジッタの大きさは、入力するPBRS(疑似ランダム信号)などのパターンに依存し変化します。

128B130Bコーディングのジッタは、評価の際に使用するPRBSのランレングスの長さとその前後のパターンに依存し、評価で一般的に使用されているPRBSの疑似ランダムパターンでは実際に起こる最悪パターンを再現できていません。

そのためランレングスが長く、DCバランスが入力パターンに依存するスクランブルのみのコーディングでは、評価の際にPRBSの疑似ランダムパターンだけではなく、ランレングスが長く、DCバランスが崩れた特殊なパターン(キラーパターン、パソロジカルパターンなど)を入力し、受信の耐性を評価するアプリケーションもあります。またこの問題に対応するため、01クロック埋め込み式SerDesの一部ではDCバランスビットを追加した規格や製品もあります。

【4】その他のSerDes

4B5B、9B10B、18B20B、256B257B、TRS(Timing Reference Signal)同期方式など、他にもさまざまなデータ変換方式を使用したSerDesの規格や製品があります。これらSerDesのシリアル方式は8B10B系と01クロック埋め込み系の2つに分類されますが、コーディングのみでDCバランスが取れる仕様は一部になります。そのためSerDes機能の導入の際は、この点も配慮して検討するとよいでしょう。

【参考文献】

・ギガビット伝送システム開発力強化集中講座 CQエレクトロニクスセミナ2012 講演資料 河西基文.

・ナショナルセミコンダクタージャパン株式会社 LVDSオーナーズマニュアル 第3版/第4版

筆者Profile

河西基文(かわにし もとふみ)/ザインエレクトロニクス シニアエキスパート

ナショナルセミコンダクタージャパンやジェナムジャパンなど、25年にわたり高速通信系半導体の製品開発・サポートおよびマーケットの開拓に従事。伝送路を含んだ半導体の高速設計手法が確立されていない時代に、LVDSオーナーズマニュアルの作成など、同マーケットの成長・普及に寄与してきた。

現在は日本のSerDes製品開発の先駆者的存在のザインエレクトロニクスで、プロダクトマーケティング・開発支援や人材育成などを行っている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

差動伝送路のケーブル・コネクターの選び方と設計上の注意

差動伝送路のケーブル・コネクターの選び方と設計上の注意

基板間や筺体間の通信に使用されるケーブルとコネクターに求められる特性やその選定方法、ピンアサインなどについて説明していきます。 LVDS PHY製品と伝送路の設計(その1)

LVDS PHY製品と伝送路の設計(その1)

LVDS PHY(物理層)製品を使用する上で必要な一般的な知識とともに、伝送路の設計方法について詳しく解説していきます。 終端方式と高速シリアルI/Fデバイス

終端方式と高速シリアルI/Fデバイス

今回は、LVDS、CML/PECL、計測器などの終端方法と、シリアル伝送デバイスの種類について解説します。 接続形態(トポロジ)と特性インピーダンス

接続形態(トポロジ)と特性インピーダンス

今回は接続形態(トポロジ)、特性インピーダンスについてです。LVDS系テクノロジーのさまざまなトポロジとその基本な構成、またPECLやCMLを使用して同機能を高速で実現する方法などについて紹介します。 高速伝送の代表的な物理層 LVDS・PECL・CML

高速伝送の代表的な物理層 LVDS・PECL・CML

今回は、高速差動伝送で使用されている代表的な物理層である「LVDS」「PECL」「CML」の特長、接続方法、用途例を紹介していきます。 差動信号伝送のメリット ――使用されている技術と注意点

差動信号伝送のメリット ――使用されている技術と注意点

高速シリアル伝送技術について基礎から学ぶ本連載。2回目は、差動信号伝送の特徴、メリットに焦点を当て、使用されている技術や注意点について解説していきます。