IGBTやCMOS ICを使った回路に隠れた“落とし穴”:Wired, Weird(2/5 ページ)

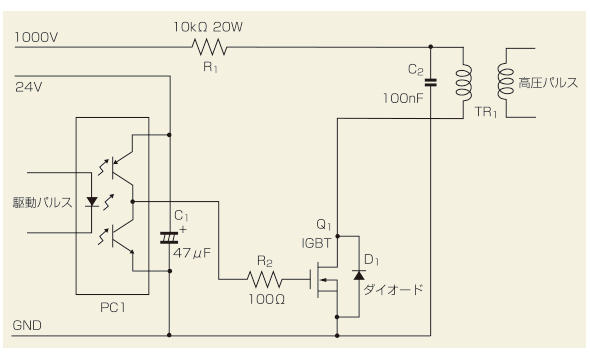

今回は、不具合が生じたIGBTやCMOS ICを使った回路例を紹介する。いずれの回路も、回路設計の“基本中の基本”をおろそかにしてしまったことが不具合の原因だった。

回路に隠れる問題は2つ

落とし穴とも言える隠れた問題は2つもある。

落とし穴の1つはIGBTのゲートの電圧だ。一般的なIGBTのゲート電圧の最大定格は±20Vであるが、図1ではゲートの最大定格電圧を超えた+24Vが印加されてしまいIGBTが劣化した可能性があった。これは、よくはまりがちな落とし穴であるが、使用するIGBTのデータシートをよく読んでゲートの駆動回路を設計してほしい。

もう1つの落とし穴がある。実はその落とし穴が、今回の不具合の原因だった。

電源を投入する順番

その落とし穴は、制御電源24Vと主回路電源1000Vを投入する順番に隠れている。先に24V電源を入れて、のちにDC1000Vを投入すれば問題はない。では、先にDC1000V電源を投入してしまうとどうなるだろうか? 多くの読者は既に理解されたと思う。FET構造のデバイスの特有の問題である。

エンジニアとして新人の頃を思い出してほしいが、電子回路の研修でFETのゲート入力やCMOS ICの入力は絶対にオープンにしてはいけないと厳しく教育されたはずだ。皆さんはその意味をきちんと理解していただろうか?

図1の回路で制御電源DC24Vを印加されていない時のフォトカプラの出力に着目しよう。高速フォトカプラは電源がない時は上側と下側のトランジスタは共にオフになっている。この2つのトランジスタの出力がIGBTのゲートに接続されている。つまり制御電源のDC24Vが印加されていなとIGBTのゲートはオープンになっている。

IGBTのゲートをオープンにしてエミッタとコレクタに主回路電源を印加するとどうなるだろう?

IGBTを販売する富士電機の技術資料に詳細な説明があったので引用して紹介しよう。

3.1 GE間オープン状態での主回路電圧印加

ゲート−エミッタ間オープン状態で主回路電圧を印加すると、IGBTの帰還容量Cresを介して電流が流れるためゲート−エミッタ間容量に電荷が充電されゲート電位が上昇します。これによりIGBTがオンして大きな電流が流れ素子が破損します。

以上のように記載されていた。下記のアドレスにあるPDFファイルの8ページを参照願いたい。

この注意事項は回路設計者が守るべき基本中の基本だ。しかし、IGBTの前段にドライバ(フォトカプラPC1)があるため、駆動回路が分かりにくくなり落とし穴にはまっていた。実際の基板には多数のIGBTが実装されていたが同一回路でありIGBTは全数劣化していた。IGBTが劣化して漏れ電流が大きくなり1000Vを印加してもIGBTの漏れ電流でコレクタ電圧が700Vに下がって、十分な高圧パルス電圧が得られていなかった。また漏れ電流で抵抗が発熱していた。

問題に対処する

図1の回路が抱える2つの問題を解消するため、まず2個のLEDを追加した。ゲート電圧が定格を少しオーバーしているので24Vの電源ラインに直列にLED2個を接続し、電源電圧を約4V下げたわけだ。このLEDは機器の電源の表示とIGBTのゲートの過電圧対策を兼ねた。

もう1つの問題を解決するための対策として抵抗を追加した。IGBTのゲートがオープンにならないようにフォトカプラ出力とGND間に4.7KΩの抵抗を追加したわけだ。この対策でIGBTの劣化はなくなり、IGBTのコレクタ電圧が上がって十分な高圧パルスが得られた。

Copyright © ITmedia, Inc. All Rights Reserved.