マイコンアーキテクチャの基本理解 〜 キャッシュ構成、エンディアン、浮動小数点、バス構成、例外処理:ハイレベルマイコン講座:【アーキテクチャ概論】(2)(1/3 ページ)

すでにマイコンを使い込まれている上級者向けの技術解説の連載「ハイレベルマイコン講座」。前回に引き続き、マイコンの「アーキテクチャ」について詳しく解説する。今回は、「キャッシュ構成」、「エンディアン(Endian)」、「浮動小数点演算」、「バス構成」、「例外処理」について詳しく解説する。

前回に引き続き、マイコンの「アーキテクチャ」について詳しく解説する。

今回は、「キャッシュ構成」、「エンディアン(Endian)」、「浮動小数点演算」、「バス構成」、「例外処理」について詳しく解説する。

キャッシュ構成

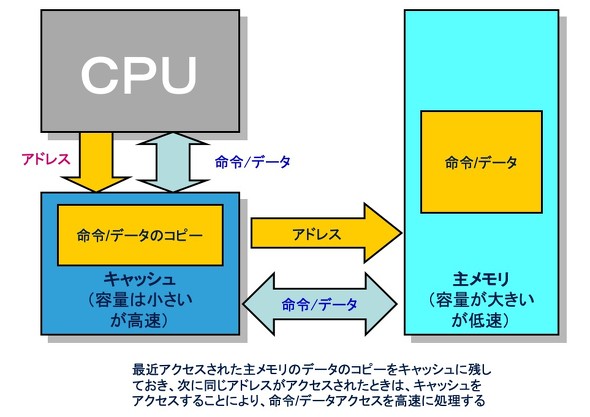

「低速ではあるが大容量の主メモリ」(以下、主メモリ)に、「高速ではあるが小容量の副メモリ」(以下、副メモリ)を組み合わせ、見かけ上、主メモリへのアクセスを高速にする手法がある。具体的には、1回でもアクセスされた主メモリの内容のコピーを副メモリに残し、次に同じアドレスがアクセスされたときは副メモリにアクセスする。これにより、実質的に主メモリへのアクセスを高速化できるわけだ。この時の「副メモリ」をキャッシュ・メモリ(Cache memory:略してキャッシュ)と呼ぶ。

キャッシュについては「Q&Aで学ぶマイコン講座(32):キャッシュとは?」で詳細に解説している。

図1に「Q&Aで学ぶマイコン講座(32):キャッシュとは?」の図1を再掲載する。

キャッシュは、配置される場所、内部構造によってカタログやマニュアルに記載されている名称が異なる。例えば、複数のキャッシュが実装されている(または、実装可能な構造になっている)場合、CPUに近い位置に配置されるキャッシュから、1次(L1)キャッシュ、2次(L2)キャッシュ、3次(L3)キャッシュ……と呼ばれる。プロセッサでは2次キャッシュ、3次キャッシュが実装されている製品もあるが、汎用マイコンでは、1次キャッシュまたはキャッシュなしの製品が多い。

また、内部構造で、統合キャッシュ(特に命令とデータを区別しないで取り扱うキャッシュ)やハーバード・キャッシュ(命令用とデータ用で、2つのキャッシュを持つ方式)に分けられる。

一方、扱うデータの種類で、命令キャッシュ(命令バス上で、命令だけを取り扱うキャッシュ)、データ・キャッシュ(データバス上で、データだけを取り扱うキャッシュ)、ブランチ・キャッシュ(命令キャッシュの中でも、ブランチ先の命令だけを取り扱うキャッシュ)、さらにはブランチ・ターゲット・アドレス・キャッシュ(BTAC:Branch Target Address Cache:ブランチ先のアドレス専用のキャッシュ)に分けられる。

エンディアン(Endian)

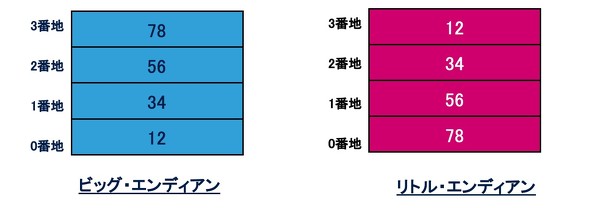

2バイト以上の数値データをメモリに格納する際に、並べる順番をエンディアン(Endian)という。上位の桁から順番にメモリに入れる場合をビッグ・エンディアンといい、下位の桁から順番に入れる場合をリトル・エンディアンという。例えば、16進数の「12 34 56 78」をメモリに格納する場合を図2に示す。

32ビットデータや16ビットデータを取り扱うときに、ビッグ・エンディアンとリトル・エンディアンでは、バイト単位のデータが入っているアドレスが異なるので、ユーザーは注意を払わなければならない。

例えば、Arm Cortex-Mプロセッサのエンディアンはデータとコードで異なる。データはリトル・エンディアンまたはビッグ・エンディアンでアクセスが可能で、コードは常時リトル・エンディアンによるアクセスになる。Cortex-Mプロセッサのモジュールには、エンディアンを設定する端子BIGENDがある。この端子を使用するとリトル・エンディアン、またはビッグ・エンディアンのいずれかを選択することができる。BIGENDピンの状態は、リセット時にロジックに取り込まれ反映される仕組みになっている。従って、リセット後にエンディアンを変更しようとしても変更できない。BIGENDの機能が有効かどうかは、Cortex-Mプロセッサを実装したマイコンの仕様によって異なる。ユーザーは、マニュアルで仕様を確認する必要がある。

Copyright © ITmedia, Inc. All Rights Reserved.