“`‘—کH‚ج“ءگ«‚ئƒVƒOƒiƒ‹ƒRƒ“ƒfƒBƒVƒ‡ƒiپ[‚ة‚و‚éƒWƒbƒ^‚ج•âڈپFچ‚‘¬ƒVƒٹƒAƒ‹“`‘—‹Zڈpچuچہپi11پjپi3/4 ƒyپ[ƒWپj

چ،‰ٌ‚ح“`‘—کH‚جŒ¸گٹ“ءگ«‚ة‚و‚éƒWƒbƒ^پA“`‘—کH‚جچإ“K‚بگفŒv•û–@پA”¼“±‘جƒfƒoƒCƒX‚ة‚و‚éƒWƒbƒ^‚ج•âڈ‚ئ‚»‚جژd‘g‚ف‚ة‚آ‚¢‚ؤگà–¾‚µ‚ؤ‚¢‚«‚ـ‚·پB

‘—گM’[پ^ژَگM’[‚ج”¼“±‘جƒfƒoƒCƒX‚ة‚و‚é“`‘—کHƒCƒ“ƒTپ[ƒVƒ‡ƒ“ƒچƒX‚جISI•âڈ

پ@ƒVƒOƒiƒ‹ƒRƒ“ƒfƒBƒVƒ‡ƒiپ[ƒfƒoƒCƒX‚ج‘—گM’[ƒGƒ“ƒtƒ@ƒVƒXƒhƒ‰ƒCƒo‚âژَگM’[ƒCƒRƒ‰ƒCƒUپ[پiCTLEپj‚جژہ‘•‚إ‚حƒ‰ƒ“ƒ_ƒ€ƒWƒbƒ^پiRJپj‚ً’لŒ¸‚·‚邱‚ئ‚ح‚إ‚«‚ـ‚¹‚ٌپB‚إ‚·‚ھپADJ‚ج1‚آ‚إ‚ ‚é“`‘—کHƒCƒ“ƒTپ[ƒVƒ‡ƒ“ƒچƒX‹Nˆِ‚جISIƒWƒbƒ^پiƒVƒ“ƒ{ƒ‹ٹشٹ±ڈآپj‚ً•âڈ‚إ‚«‚ـ‚·پBپ@ˆب‰؛‚ة‚»‚ج•û–@‚ئ“®چى‚ة‚آ‚¢‚ؤگà–¾‚µ‚ؤ‚¢‚«‚ـ‚·پB

ڈo—حƒhƒ‰ƒCƒo‚ة‚و‚éƒCƒ“ƒTپ[ƒVƒ‡ƒ“ƒچƒX‚ج•âڈ پ` ƒvƒٹƒGƒ“ƒtƒ@ƒVƒXپ^ƒfƒBƒGƒ“ƒtƒ@ƒVƒX

پ@ƒvƒٹƒGƒ“ƒtƒ@ƒVƒXپ^ƒfƒBƒGƒ“ƒtƒ@ƒVƒXƒhƒ‰ƒCƒo‚ئ‚à“`‘—کH‚ً’ت‰ك‚µ‚½ژَگM’[‚إ‚جژü”gگ”ˆث‘¶‚جŒ¸گٹ‚ًڈo—ح’[‚إ•â‚¤‹Zڈp‚إ‚·پB

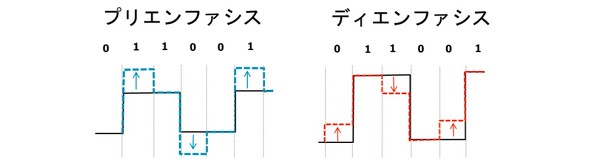

پ@ƒPپ[ƒuƒ‹پAƒRƒlƒNƒ^پ[پAٹî”آ‚ب‚ا‚ج“`‘—کH‚جƒCƒ“ƒTپ[ƒVƒ‡ƒ“ƒچƒX‚ة‚و‚ء‚ؤپAژَگM’[ƒfƒoƒCƒX‚ج“ü—حگMچ†‚حچ‚ژü”g‚ھŒ¸گٹ‚µگU•‚ھڈ¬‚³‚‚ب‚è‚ـ‚·‚ھپA’لژü”g‚حچ‚ژü”g‚ئ”نٹr‚µŒ¸گٹ—ت‚حڈ‚ب‚¢ڈَ‘ش‚إ‚·پB‚±‚جٹآ‹«‚ج‹t“ءگ«‚ة‚ب‚é‚و‚¤‚ة‚ ‚ç‚©‚¶‚ك‘—گM’[‚إچ‚ژü”gگ¬•ھ‚ً’لژü”gگ¬•ھ‚ئ”نٹr‚µ‚ؤ‘ه‚«‚‚µپAژَگM’[‚إ‚جISIƒWƒbƒ^‚ً•âڈ‚·‚é•û–@‚ھƒvƒٹƒGƒ“ƒtƒ@ƒVƒX‚ئƒfƒBƒGƒ“ƒtƒ@ƒVƒX‚إ‚·پB

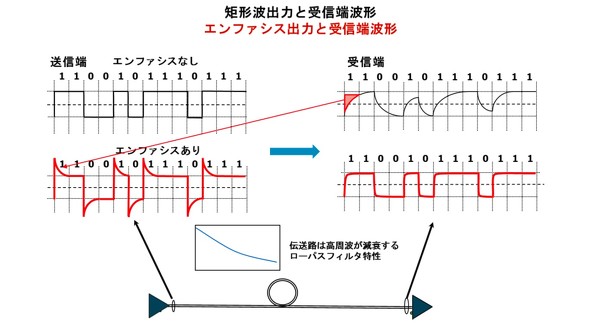

پ@گ}6‰Eڈم‚جچ•گü‚جژَگM’[”gŒ`‚حپA“`‘—کH‚جƒچپ[ƒpƒXƒtƒBƒ‹ƒ^پ[“ءگ«‚ة‚و‚è‘—گM’[‹éŒ`”g‚جچ‚ژü”g‚ھŒ¸گٹ‚µپAƒGƒbƒW•”•ھ‚جƒGƒlƒ‹ƒMپ[‚ھڈ¬‚³‚‚ب‚ء‚ؤ‚¢‚ـ‚·پB

پ@گ}6چ¶‰؛‚جگشگü‘—گM’[‚جƒnƒCƒpƒXƒtƒBƒ‹ƒ^پ[‚ً’ت‚µ‚½‚و‚¤‚بڈo—ح‚جƒGƒ“ƒtƒ@ƒVƒX”gŒ`‚حپAژَگM’[‚إچ•گü‚جچ‚ژü”g‚ھŒ¸گٹ‚µ‚½ƒGƒbƒW•”•ھ‚ج”gŒ`‚ًگط‚èژو‚ء‚ؤ‰ء‚¦‚½‚و‚¤‚بŒ`‚ة‚ب‚ء‚ؤ‚¨‚èپAژَگM’[‚إŒ¸گٹ‚·‚éچ‚ژü”gƒGƒlƒ‹ƒMپ[‚ً‘—گM’[‚إ‹’²‚µ‚½ڈo—ح‚ئ‚·‚éژ–‚إپAژَگM’[‚جISIƒWƒbƒ^‚ً•âڈ‚µ‚ؤ‚¢‚ـ‚·پB

پ@ƒvƒٹƒGƒ“ƒtƒ@ƒVƒX‚ئƒfƒBƒGƒ“ƒtƒ@ƒVƒX‚ح‚ا‚؟‚ç‚à‘ٹژ—Œ`‚إ‚·پB‘¬“x‚ج’ل‚¢ƒAƒvƒٹƒPپ[ƒVƒ‡ƒ“‚إ‚حƒGƒbƒWƒŒپ[ƒg‚ھ1UIپiƒ†ƒjƒbƒgƒCƒ“ƒ^پ[ƒoƒ‹پj‚ئ”نٹr‚µڈ\•ھ—]—T‚ھ‚ ‚èگU•‚ًڈم‚°‚邱‚ئ‚ھ‰آ”\‚ب‚½‚كگ}7چ¶‚جƒvƒٹƒGƒ“ƒtƒ@ƒVƒX‚ًژg—p‚µپAگ”پ`گ”ڈ\ƒMƒKƒrƒbƒg/•bپiGbpsپj‚ج‘رˆو‚إ‚حƒGƒbƒWƒŒپ[ƒg‚ھچ‚‘¬‚ب‹éŒ`”g‚ة‚³‚ç‚ةƒGƒbƒWƒŒپ[ƒg‚ًڈم‚°‚½چ‚ژü”gگ¬•ھ‚ج’ا‰ء‚حچ¢“ï‚ب‚½‚كگ}7‰E‚ج’لژü”g•”•ھ‚ًŒ¸گٹ‚³‚¹‚éƒfƒBƒGƒ“ƒtƒ@ƒVƒX‚جژg—p‚ھˆê”ت“I‚إ‚·پB

پ@‚ـ‚½ƒhƒ‰ƒCƒo‚جƒGƒ“ƒtƒ@ƒVƒX—ت‚حگU•“dˆ³‚à‚µ‚‚حƒsپ[ƒNگU•‚ئˆہ’è•”•ھ‚جگU•‚جچ·‚جƒfƒVƒxƒ‹پidBپj‚إ•\ژ¦‚³‚ê‚ـ‚·پB

پ@گ}6‚ئگ}7‚جƒGƒ“ƒtƒ@ƒVƒX”gŒ`‚ً”نٹr‚·‚é‚ئپAگ}6‚جگشگüڈo—ح”gŒ`‚إ‚ح‹éŒ`”g‚ةƒnƒCƒpƒXƒtƒBƒ‹ƒ^پ[‚ً’ت‚µ‚½ƒAƒiƒچƒO“I‚بƒGƒ“ƒtƒ@ƒVƒX”gŒ`‚إپAƒPپ[ƒuƒ‹‚جƒچپ[ƒpƒXƒtƒBƒ‹ƒ^پ[“ءگ«‚ج‹t“ءگ«‚ة‚و‚è—‘z“I‚ةژَگM’[‚جISIƒWƒbƒ^‚ً•âگ³‚إ‚«‚ؤ‚¢‚ـ‚·پB‚µ‚©‚µپAƒVƒٹƒAƒ‰ƒCƒU‚ب‚ا‚ةژہ‘•‚³‚ê‚éگ}7‚ج‚و‚¤‚بƒfƒWƒ^ƒ‹ڈˆ—‚ئƒfپ[ƒ^ƒŒپ[ƒg‚ةˆث‘¶‚µ‚½ƒGƒ“ƒtƒ@ƒVƒX”gŒ`‚إ‚حپA–{—ˆ•K—v‚ب“`‘—کH“ءگ«‚ج‹t“ءگ«‚ج—‘z“I‚بƒnƒCƒpƒXƒtƒBƒ‹ƒ^پ[“ءگ«‚ًچى‚邱‚ئ‚ھ“‚پAƒGƒ“ƒtƒ@ƒVƒX—ت‚ً‘ه‚«‚‚µ‚·‚¬‚é‚ئژَگM’[‚جƒWƒbƒ^‚ً‘‚â‚·Œ´ˆِ‚ة‚à‚ب‚è‚ـ‚·پB

Copyright © ITmedia, Inc. All Rights Reserved.