伝送路の特性とシグナルコンディショナーによるジッタの補償:高速シリアル伝送技術講座(11)(4/4 ページ)

今回は伝送路の減衰特性によるジッタ、伝送路の最適な設計方法、半導体デバイスによるジッタの補償とその仕組みについて説明していきます。

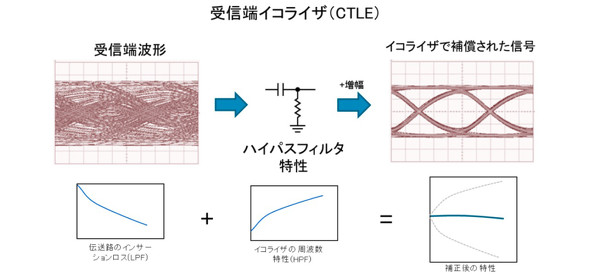

受信端イコライザー(CTLE)による伝送路インサーションロスのISI補償

受信端でのインサーションロスの補償ではCTLE(Continuous Time Linear Equalizer)を使用します。

CTLEの動作原理は、図8のように伝送路のインサーションロス特性の逆特性をハイパスフィルターで補償してISIジッタを低減しています。

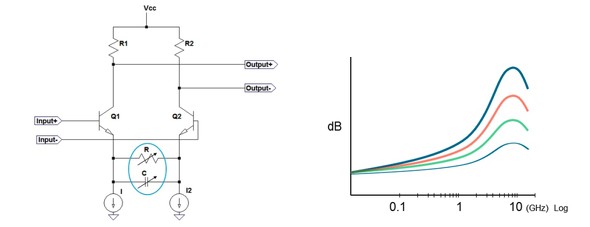

上記のハイパスフィルターだけでは信号は減衰するため、実際は図9左のような差動増幅器に可変の抵抗/容量(青丸部分)を付け、2つの定電流源を組み合わせて制御し、伝送路で減衰する高周波成分をアナログ的にブーストしています。高周波の入力では回路中のキャパシター(C)は低インピーダンスになり、Q1、Q2それぞれのトランジスタに流れる定電流源からの電流値が2倍(I+I2)になっていることが分かります。

CTLEのACレスポンス特性は一般的に図9右のようにログ(Log)で表示されることが多く、伝送路のインサーションロスはリニア(Linear)で表示されています。そのためCTLEのACレスポンスをLinearで表示して比較すると、伝送路の逆特性に合致しているかどうかがよく分かります。

これら出力プリエンファシス/ディエンファシスと入力CTLEのイコライザーの伝送路損失補償の機能は高速のSerDesやリタイマー(CDR)製品の多くに内蔵されており、また高速伝送向けの汎用リドライバや差動バッファ、リピーターと呼ばれる単機能のデバイスにもこの機能が内蔵され提供されています。

今回は伝送路の周波数特性とシグナルコンディショナーデバイスのエンファシス出力とアナログのCTLEでの補償動作について説明しました。送信側のエンファシス出力と受信側のアナログのイコライザーとも、インサーションロスにより減衰する高周波をブーストする似た動作をしていることが理解できたのではないでしょうか。

次回はデジタル処理のイコライザーである送信端のFFE(Feed Forward Equalizer)/受信端のDFE(Decision Feedback Equalizer)と数〜数十Gbpsで使用されるCML系の高速差動伝送路の設計手法について説明していきます。

参考文献

・Keysight Design Forum 2018 V-by-One® US Signal Integrity technology講演資料 河西基文.

・ナショナルセミコンダクタージャパン株式会社 LVDSオーナーズマニュアル 第3版/第4版

筆者Profile

河西基文(かわにし もとふみ)/ザインエレクトロニクス シニアエキスパート

ナショナルセミコンダクタージャパンやジェナムジャパンなど、25年にわたり高速通信系半導体の製品開発・サポートおよびマーケットの開拓に従事。伝送路を含んだ半導体の高速設計手法が確立されていない時代に、LVDSオーナーズマニュアルの作成など、同マーケットの成長・普及に寄与してきた。

現在は日本のSerDes製品開発の先駆者的存在のザインエレクトロニクスで、プロダクトマーケティング・開発支援や人材育成などを行っている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

高速インタフェースで使用されるSerDes 〜 種類と特長、その歴史

高速インタフェースで使用されるSerDes 〜 種類と特長、その歴史

代表的な3種類のシリアライザ(Serializer)とデシリアライザ(De-serializer)の機能と歴史について説明していきます。 差動伝送路のケーブル・コネクターの選び方と設計上の注意

差動伝送路のケーブル・コネクターの選び方と設計上の注意

基板間や筺体間の通信に使用されるケーブルとコネクターに求められる特性やその選定方法、ピンアサインなどについて説明していきます。 LVDS PHY製品と伝送路の設計(その1)

LVDS PHY製品と伝送路の設計(その1)

LVDS PHY(物理層)製品を使用する上で必要な一般的な知識とともに、伝送路の設計方法について詳しく解説していきます。 終端方式と高速シリアルI/Fデバイス

終端方式と高速シリアルI/Fデバイス

今回は、LVDS、CML/PECL、計測器などの終端方法と、シリアル伝送デバイスの種類について解説します。 接続形態(トポロジ)と特性インピーダンス

接続形態(トポロジ)と特性インピーダンス

今回は接続形態(トポロジ)、特性インピーダンスについてです。LVDS系テクノロジーのさまざまなトポロジとその基本な構成、またPECLやCMLを使用して同機能を高速で実現する方法などについて紹介します。 高速伝送の代表的な物理層 LVDS・PECL・CML

高速伝送の代表的な物理層 LVDS・PECL・CML

今回は、高速差動伝送で使用されている代表的な物理層である「LVDS」「PECL」「CML」の特長、接続方法、用途例を紹介していきます。 差動信号伝送のメリット ――使用されている技術と注意点

差動信号伝送のメリット ――使用されている技術と注意点

高速シリアル伝送技術について基礎から学ぶ本連載。2回目は、差動信号伝送の特徴、メリットに焦点を当て、使用されている技術や注意点について解説していきます。