ΔΣADCのノイズ測定と絶対/相対ノイズパラメーター比較:アナログ設計のきほん【ADCとノイズ】(2)(3/3 ページ)

前回に引き続き、ADコンバーターにおけるノイズの基本を説明していきます。今回はADCノイズの測定方法、データシートにおけるノイズ仕様、絶対ノイズパラメーターと相対ノイズパラメーターの比較を紹介します。

絶対ノイズパラメーターと相対ノイズパラメーターの比較

表1で示した全ての式について重要な特徴は、なんらかの値の比が含まれることです。これらを「相対パラメーター」と定義します。この名前で分かるように、これらのパラメーターは、ある絶対値に対する相対値としてのノイズ特性指標を表します。ここでの絶対値は通常、入力信号(キャリアに対するデシベル[dBc])またはフルスケール範囲(フルスケールに対するデシベル[dBFS])です。

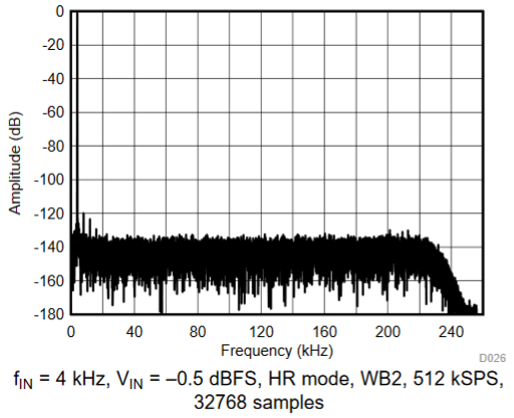

図5に、−0.5dBFSの入力信号を使用したADS127L01の出力スペクトルを示します。この場合フルスケールは2.5Vです。同じフルスケール電圧を基準としないシステム入力信号を選択する場合、または入力信号振幅がデータシートで定義されている値と異なる場合は、それ以外の入力条件が同じだとしても、必ずしもデータシート通りの性能が得られるとは期待できません。

同様に、DCノイズパラメーターについては、表1から与えられた動作条件および、ADCのFSRの時に、有効分解能はADCの入力換算ノイズ性能に関連することが分かります。FSRはADCの基準電圧に依存するため、データシートで使用されるものと異なる基準電圧を使用すると、ADCの性能指標に与えます。

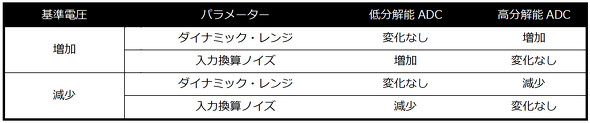

高分解能ADCでは、基準電圧が増加すると、最大入力ダイナミックレンジが増加しますが、入力換算ノイズは変化しません。これは、高分解能ADCノイズ特性が基準電圧にほとんど依存しないためです。最下位ビット(LSB)サイズによって支配される低分解能ADCの場合、入力ダイナミックレンジはほぼ同じままで、基準電圧を上げると実際に入力換算ノイズが増加します。表2は、これらの効果をまとめたものです。

したがって、ADCの最大ダイナミックレンジを規定するために、ほとんどのADCのメーカーはFSRが最大であると想定して有効分解能とノイズフリー分解能を規定します。つまり言い換えると、最大FSR(またはメーカーがADCの規定に使用した特定のFSR)を使用しないシステムの場合は、データシートで規定された有効分解能やノイズフリー分解能の値を達成することを期待できません。

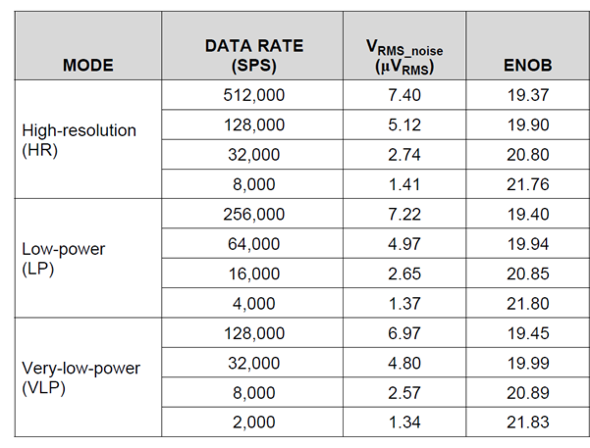

データシートのノイズが2.5Vの基準電圧を使って規定されているADCで1Vの基準電圧を使うことによってこの点を説明しましょう。引き続きADS127L01を例にします。図6に示すように、超低消費電力(VLP)モードで2.5Vの基準電圧と2kSPSのデータレートを使用すると、入力換算ノイズが1.34μVRMS、有効分解能が21.83ビットになることが分かります。

しかし、1Vの基準電圧を使用するとFSRが2Vに減少します。この値を使用して、式1に与えられる新しい予想有効分解能(ダイナミックレンジ)を計算できます。

基準電圧を変更するとADCのFSRが減少し、結果としてその有効分解能(ダイナミックレンジ)はデータシートの値と比べて1.3ビット以上減少します。式2は、この分解能の損失を一般化したものです。

ここで「% utilization(パーセント使用率)」とは、実際のFSRとADCのノイズにより特性化されたSNRの比です。

この見かけの分解能損失は高分解能のデルタ-シグマADCを使用することの欠点のように思われるかもしれませんが、FSRが減少しても入力換算ノイズはそうならないことを思い出してください。したがって、絶対ノイズパラメーター、または直接測定されたパラメーターを使用してADCノイズ解析を実行することをお勧めします。絶対ノイズパラメーターを使用することは、相対雑音パラメーターの入力信号および基準電圧特性への依存性を排除します。さらに、絶対パラメーターは、ADCノイズとシステムノイズの関係を単純化します。

ADCノイズ分析には、入力換算ノイズを使用することを推奨します。ADC性能の定義に入力換算ノイズを使用することは一般的ではないため、この用語を太字で表しました。実際、エンジニアの大部分は、もっぱら有効分解能やノイズフリー分解能などの相対パラメーターに関してのみ話をしており、これらの値を最大化できないときを非常に気にかけています。結局のところ、16ビットの有効分解能を実現するために24ビットのADCを使う必要がある場合、ADCが実際には発揮できない性能にお金を払っているように見えます。

しかし、有効分解能が16ビットであるからといって、FSRのうちどれくらいが使用されるかは必ずしも分かりません。16ビットの有効分解能しか必要ないかもしれませんが、最小入力信号が50nVの場合、16ビットのADCで、それを分解することはできません。したがって、高分解能のデルタ-シグマADCの真の利点は、それが提供する低レベルの入力換算ノイズです。有効分解能が重要でないというわけではありません。単にシステムをパラメーター化するベストな方法ではないだけです。

つまりは、ADCが最小と最大の入力信号の両方を分解できなければ、SNRや有効分解能を最大化しても意味がありません。また有効分解能と違って、ADCの必要な入力換算ノイズはシステム仕様から直接簡単に求めることができます。このため、入力換算ノイズ分析はシステムの変更に対してより柔軟に対応できます。それに加えて、さまざまなADCを簡単に比較できるため、どのアプリケーションに対してもそれに適したADCを選択できます。

次回、連載第3回では、抵抗性ブリッジ設計の例を詳しく見ていきます。相対と絶対の両方のノイズパラメーターを使用してシステム分解能を定義し、それぞれの有効性を説明します。各パラメーターの種類がADCの比較と選択に与える影響も説明します。

重要なポイント

以下は、デルタ-シグマADC内のノイズをよりよく理解する上で重要なポイントをまとめたものです。

- 異なる種類のノイズを数値化する別個の測定方法がある

- ACノイズ特性の測定には、AC信号を利用したテストを使用する

- DCノイズ特性の測定には、入力短絡テストを使用する

- ノイズ測定の種類は通常、ADCのエンドアプリケーションで決まる

- 有効/ノイズフリー分解能指標とは?一般的に、入力信号=FSRと想定する

- 2種類のノイズパラメーターが存在する

- 相対−測定値の比を用いて算出する

- 絶対−直接測定する

- 入力換算ノイズはADCの分解能(測定可能な最小信号)の絶対値である。ノイズフリービットと有効分解能は、ADCのダイナミックレンジを表す相対パラメーターである

著者紹介

ブライアン・リゾン(Bryan Lizon)

テキサス・インスツルメンツ 高精度ADC製品プロダクト・マーケティング・エンジニア

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

デルタ-シグマADC内のノイズの概要

デルタ-シグマADC内のノイズの概要

デルタ-シグマADCのノイズに関する包括的な理解を深めるために、代表的なシグナルチェーンの一般的なノイズ源を調べ、ノイズを低減して高精度の測定を維持する手法を解説していきます。第1回は、ADCノイズの基本を重点的に見ていきながら、「ノイズとは何なのか」「高分解能ADCと低分解能ADCではノイズにどのような違いがあるか」などの疑問について、詳しく説明していきます。 A-Dコンバーターの「ノイズ・スペクトル密度」を理解する

A-Dコンバーターの「ノイズ・スペクトル密度」を理解する

信号アクイジションシステムについては、数十年にわたってより広い帯域幅が求められる状況が続いています。その結果、高速A-Dコンバーター(ADC)で最も重視される性能項目にも緩やかな変化が生じています。それに伴い、ADCの性能は、従来とは異なる方法で測定されるようになってきました。 IoTにおける“精度”の重要性

IoTにおける“精度”の重要性

IoT(モノのインターネット)では、高精度にデータを計測、センシングする必要があります。高い精度での計測、センシングは、IoTにさまざまな利点をもたらすためです。ここでは、いかにIoTにおいて、計測/センシングの精度が重要であるかを事例を挙げつつ、考察していきます。 オペアンプのダイナミック応答の検討(2) タイプ2補償回路の伝達関数

オペアンプのダイナミック応答の検討(2) タイプ2補償回路の伝達関数

第2部では、2つの極の概要とそれらがフィルターの最終的な性能に対してもたらす歪みについて考察しながら、タイプ2の補償回路の伝達関数を決定する方法を説明します。 オペアンプのダイナミック応答の検討(1) タイプ2補償回路の使用時

オペアンプのダイナミック応答の検討(1) タイプ2補償回路の使用時

補償回路は、理想的な特性を想定したオペアンプを中心に構築したアクティブ回路が使用されます。ですが、理想的なオペアンプを想定した計算は成立せず、最終的にゲインと位相の深刻な歪みを招く結果になります。開ループゲインと、低周波および高周波にある2つの極が全体的な応答の形状をどのように規定するかが明らかになると、適切なオペアンプを選択できます。 高速、高電圧絶縁のための絶縁LVDSバッファ

高速、高電圧絶縁のための絶縁LVDSバッファ

絶縁と長い距離にわたる高速相互接続を両立する場合、絶縁LVDS(低電圧差動信号)バッファが有効です。そこで、絶縁LVDSバッファの活用例を紹介するとともに、昨今の絶縁要件などを考察し、最新の絶縁LVDSバッファソリューション例を紹介します。